Arm

®

Compiler

Version 6.6

armclang Reference Guide

Copyright © 2014–2017, 2019, 2020 Arm Limited or its affiliates. All rights reserved.

DUI0774K

Arm

®

Compiler

armclang Reference Guide

Copyright © 2014–2017, 2019, 2020 Arm Limited or its affiliates. All rights reserved.

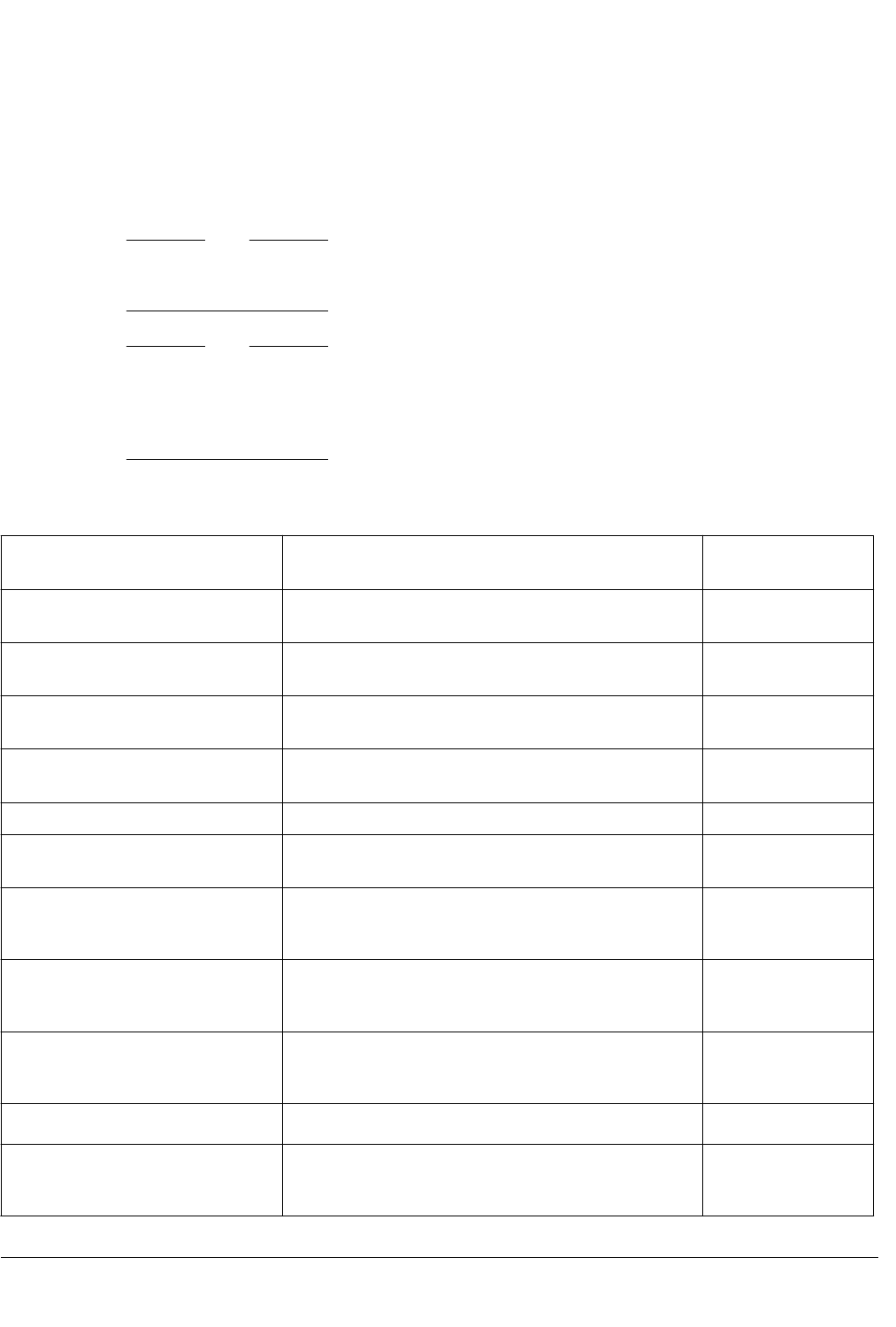

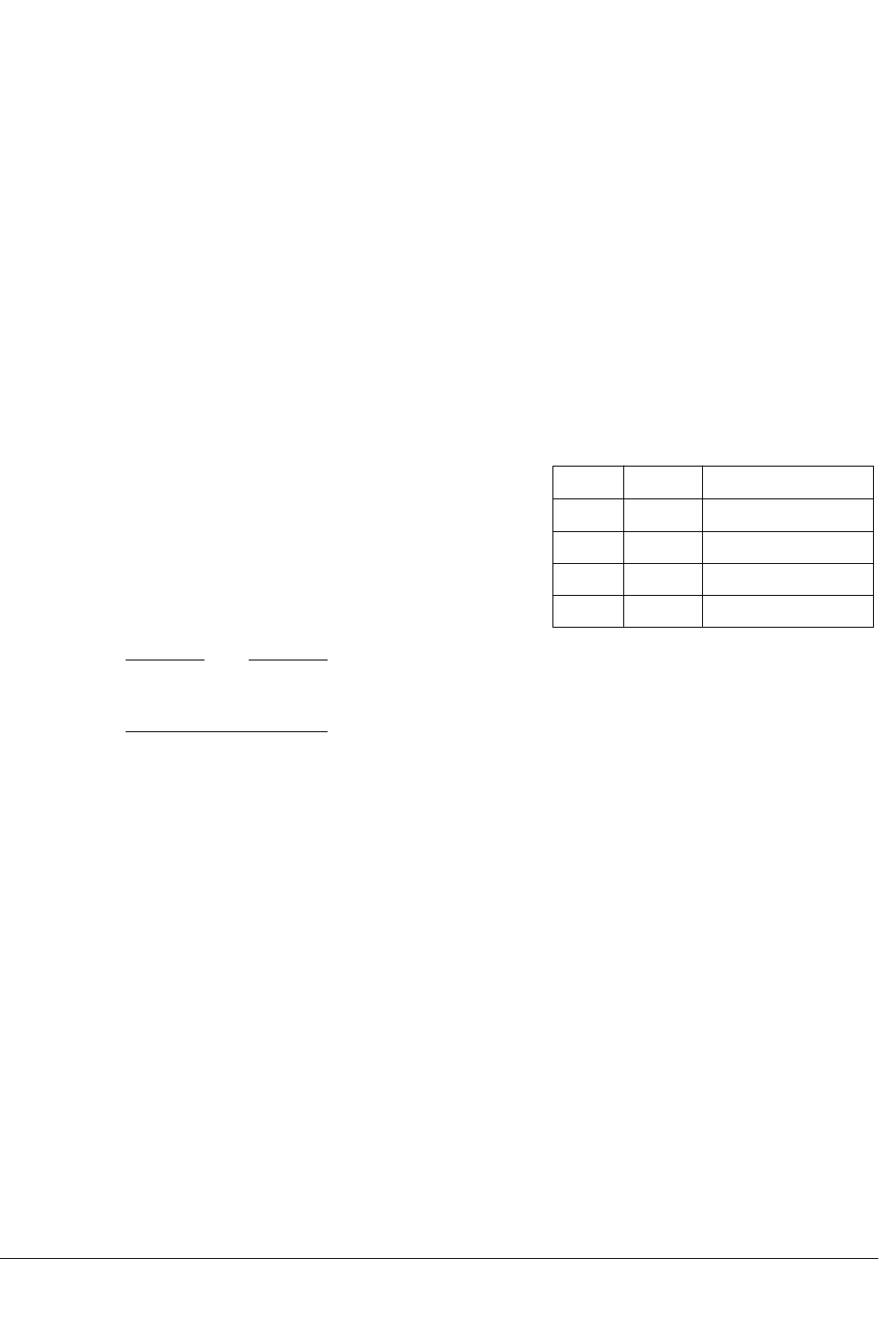

Release Information

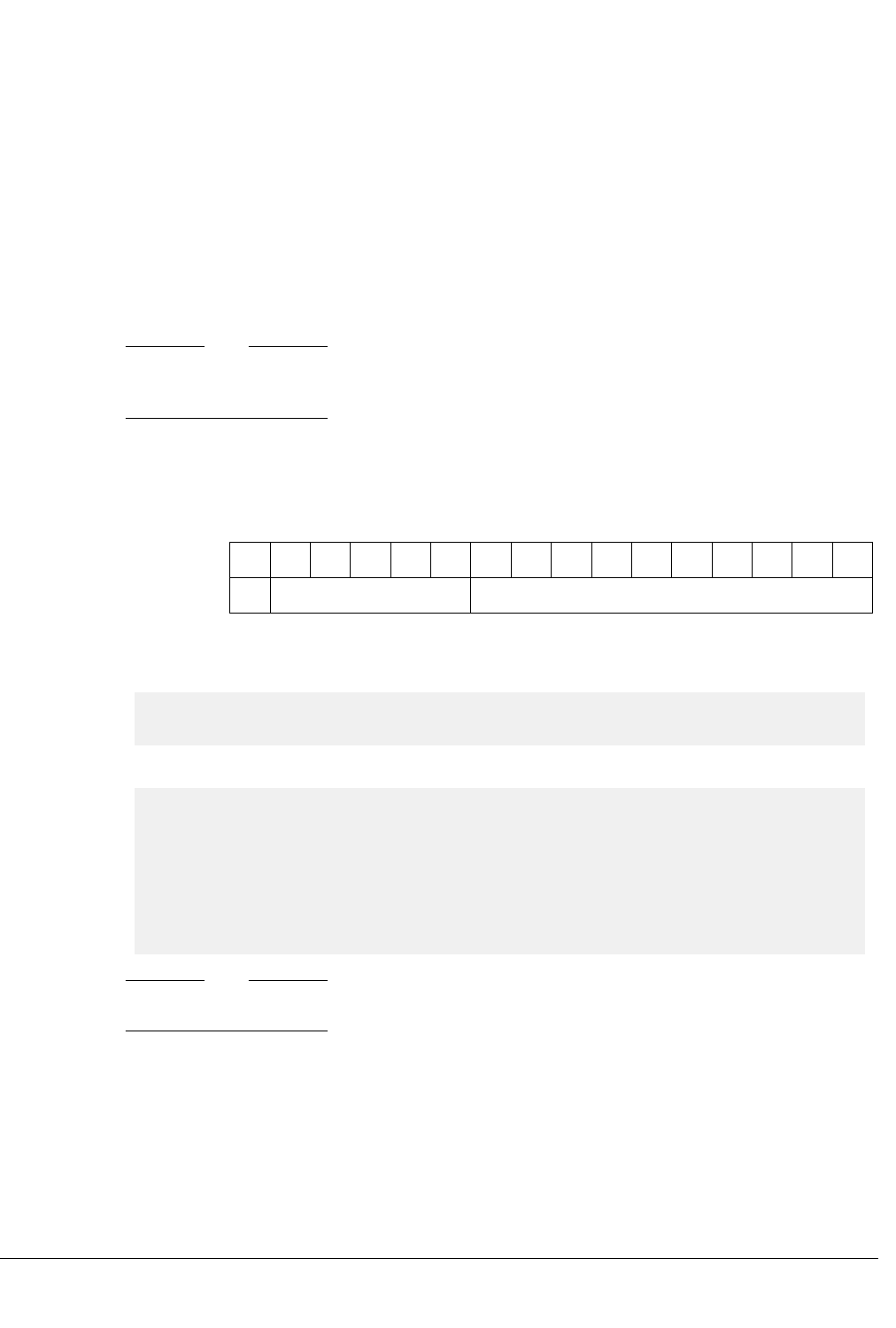

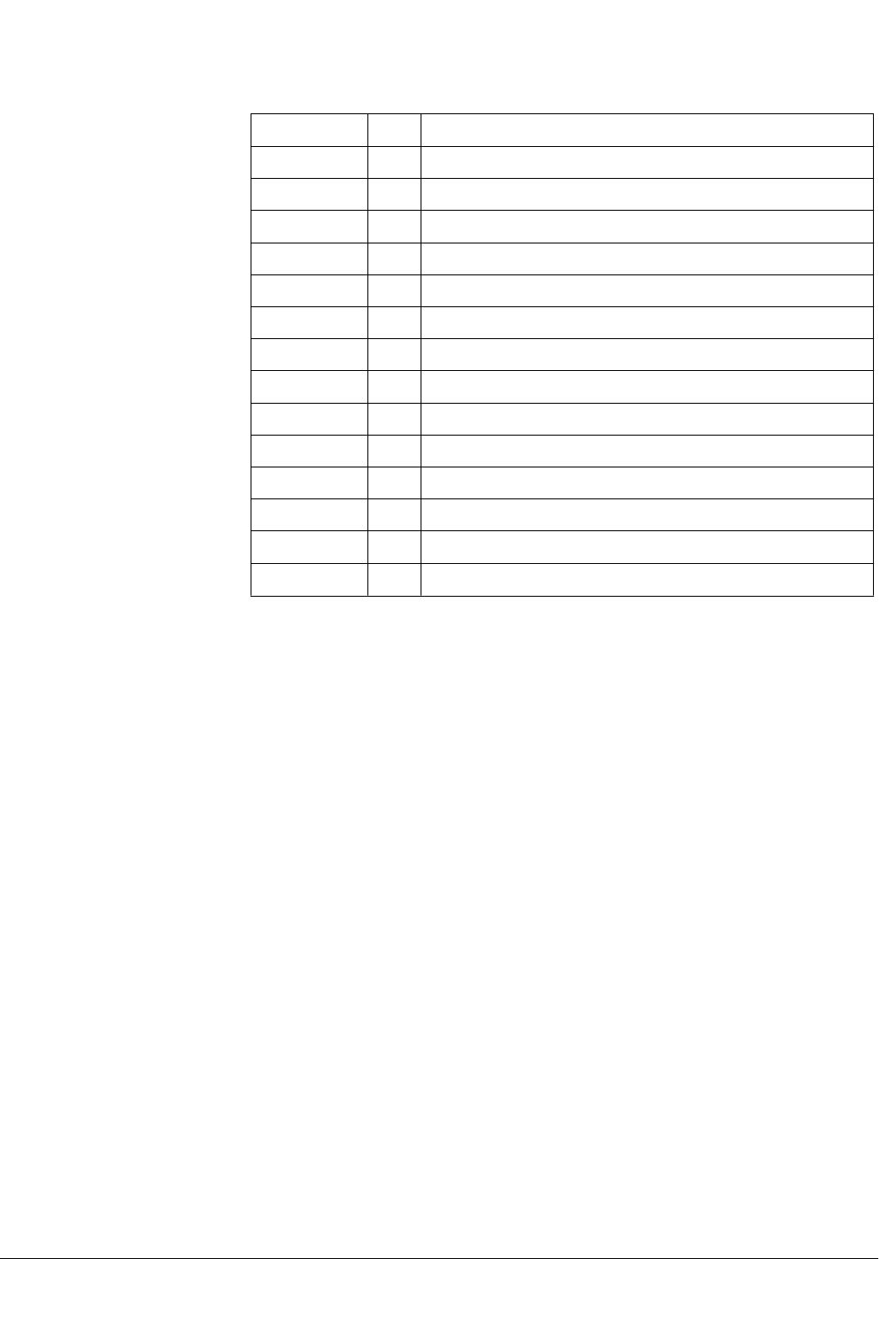

Document History

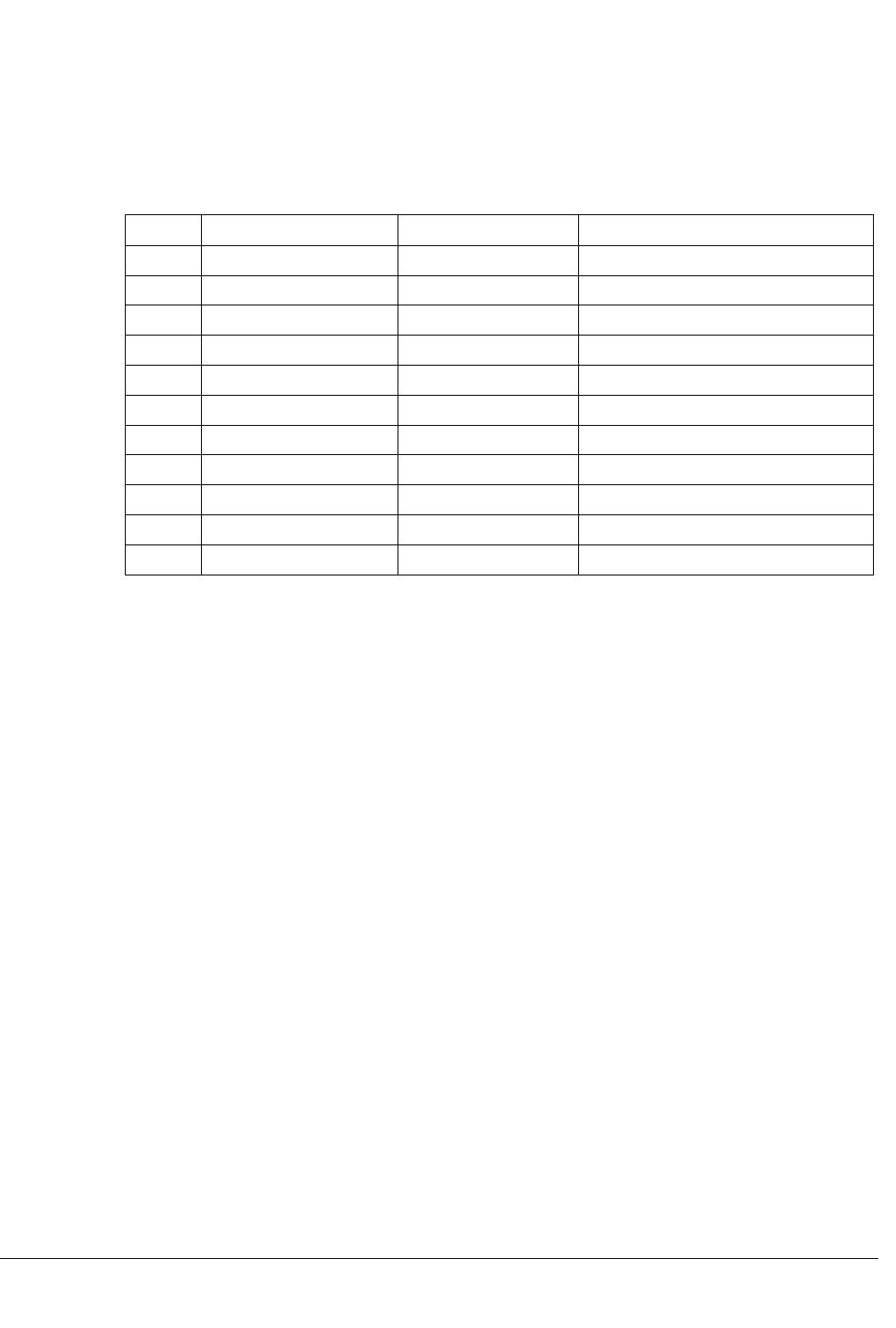

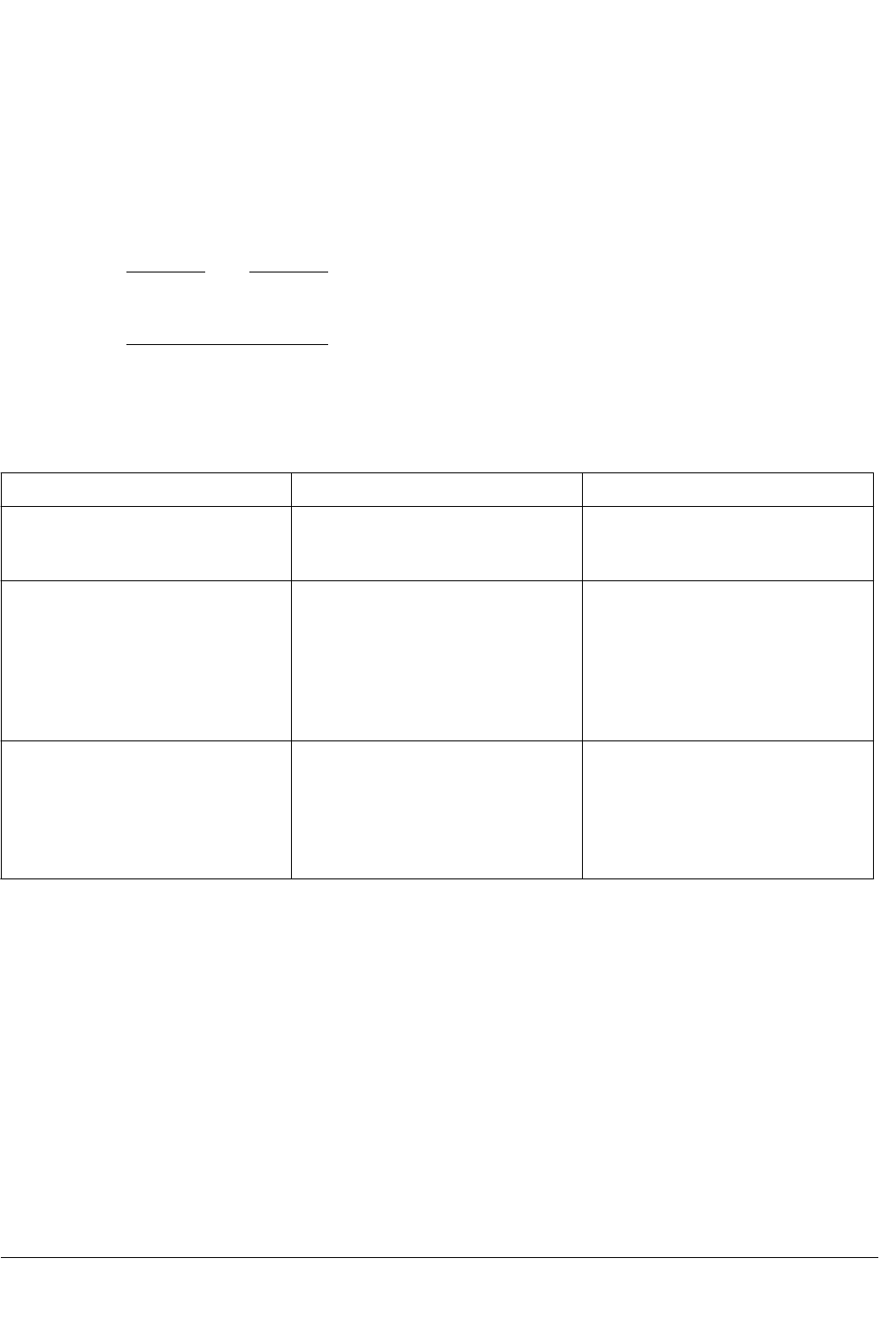

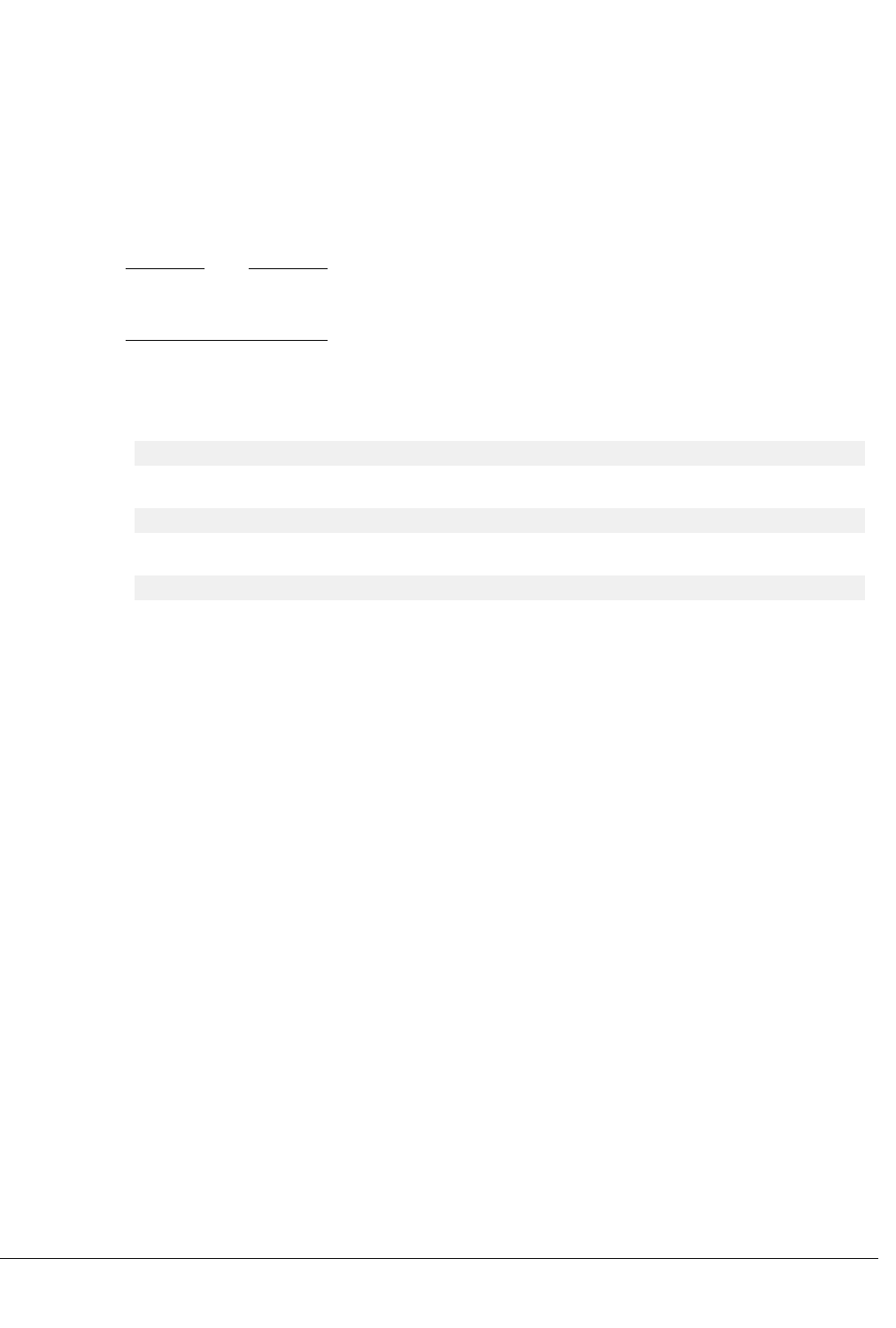

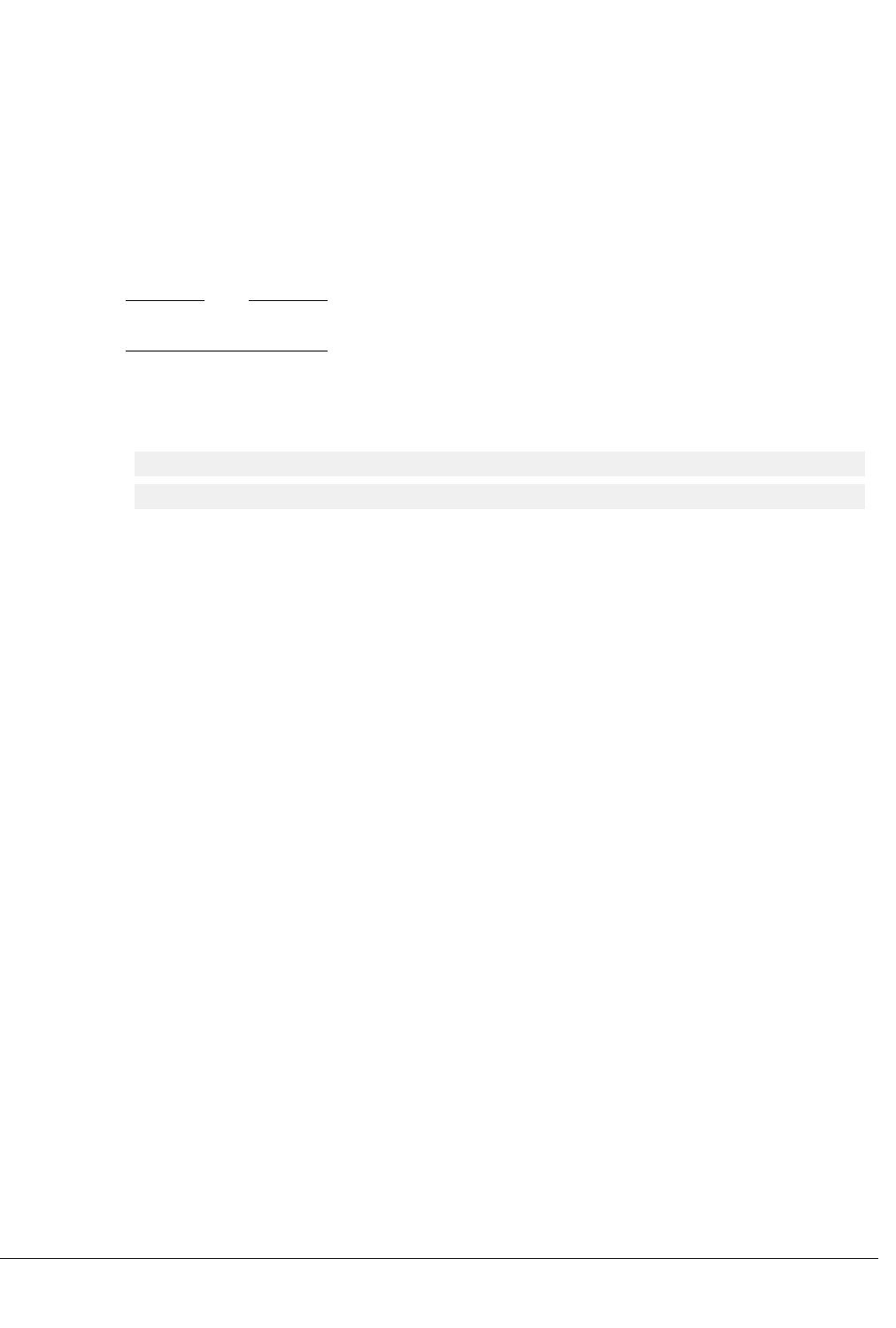

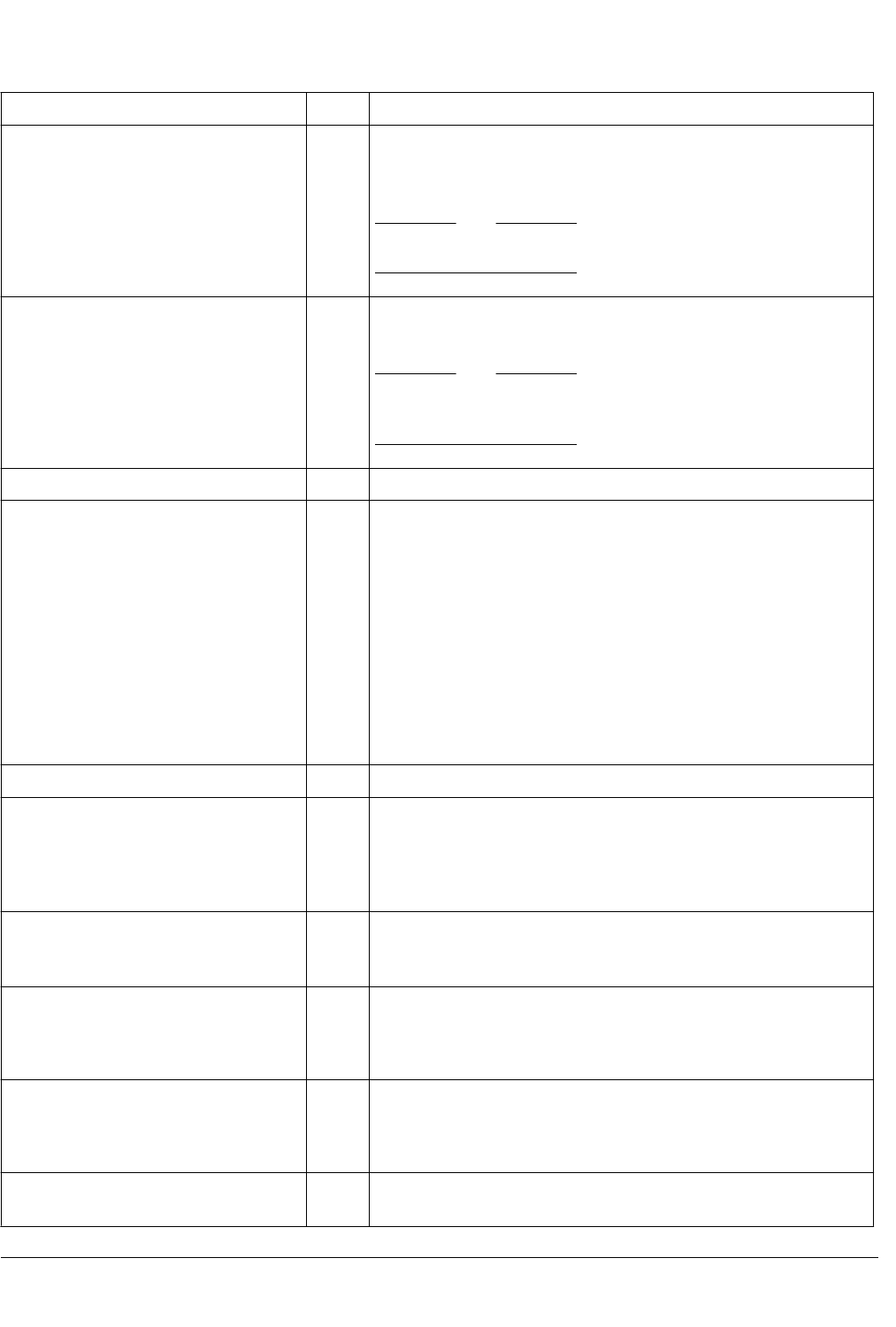

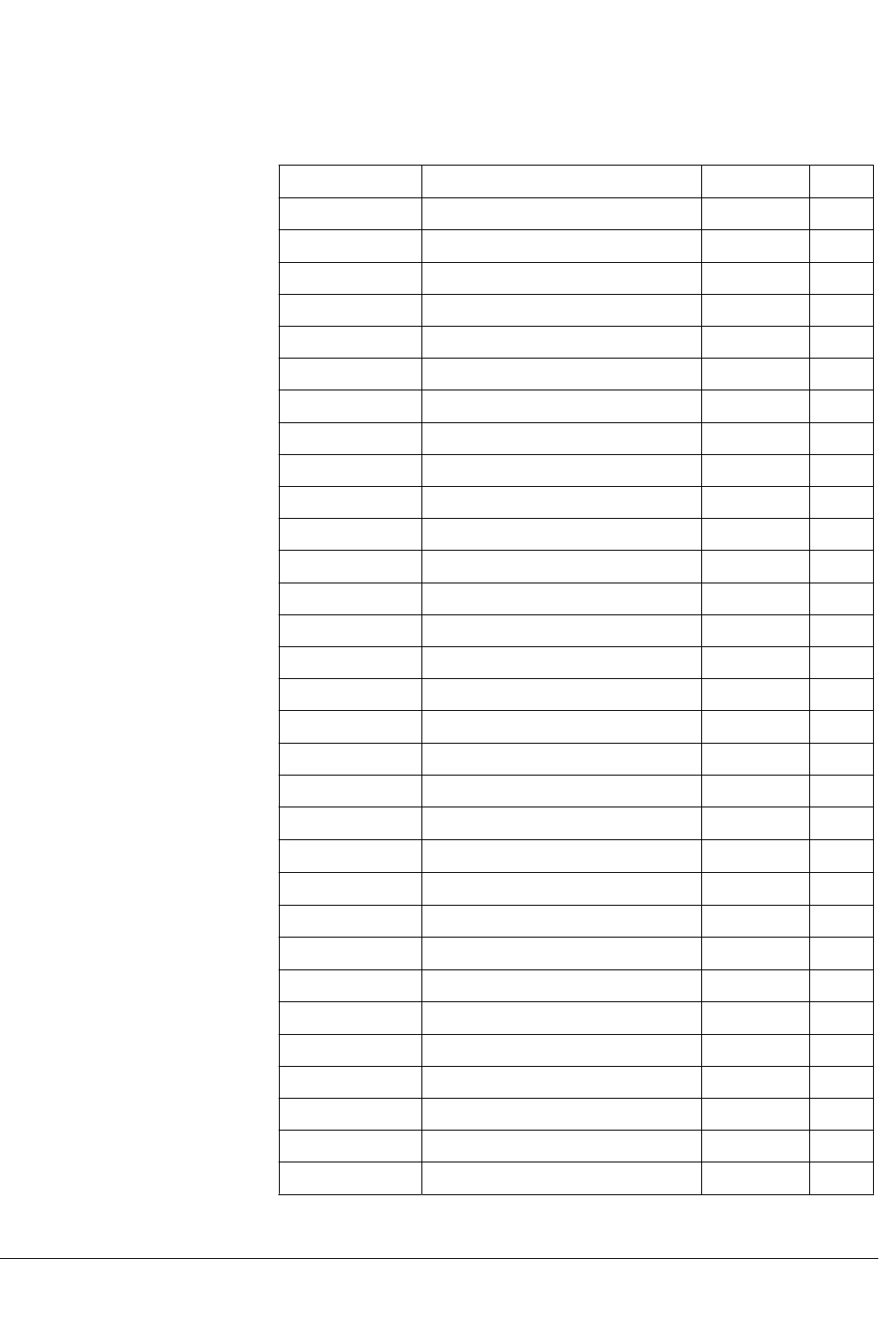

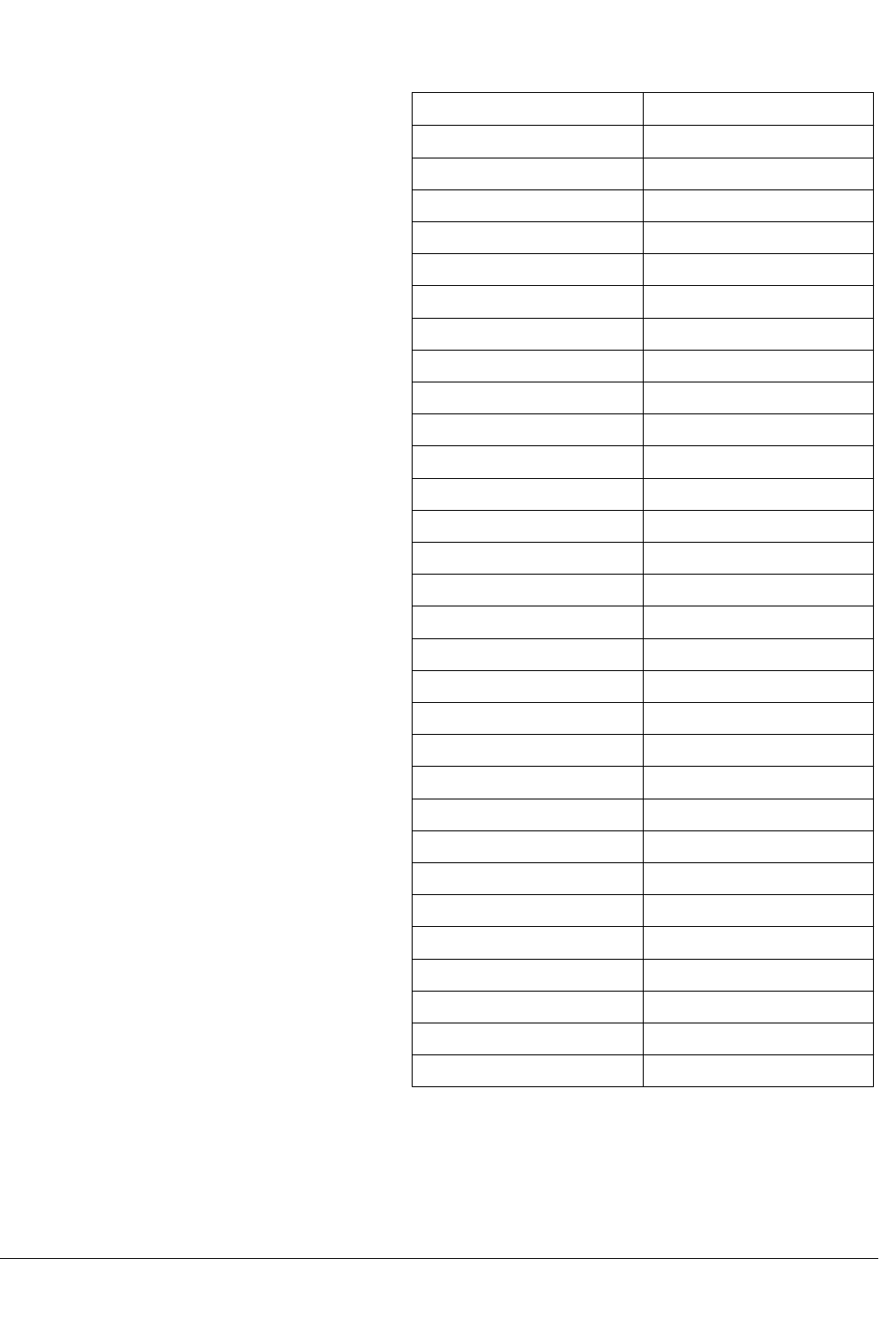

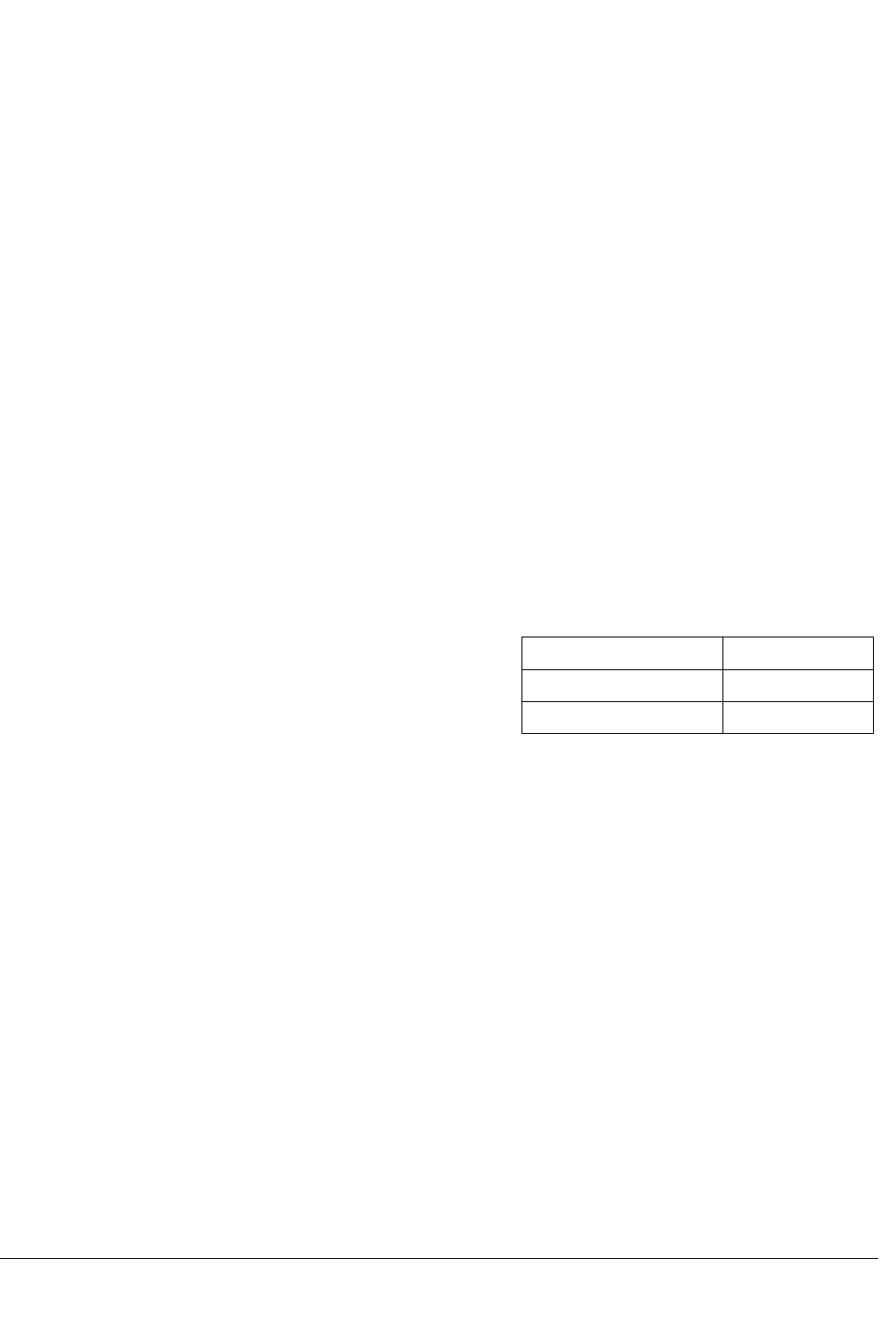

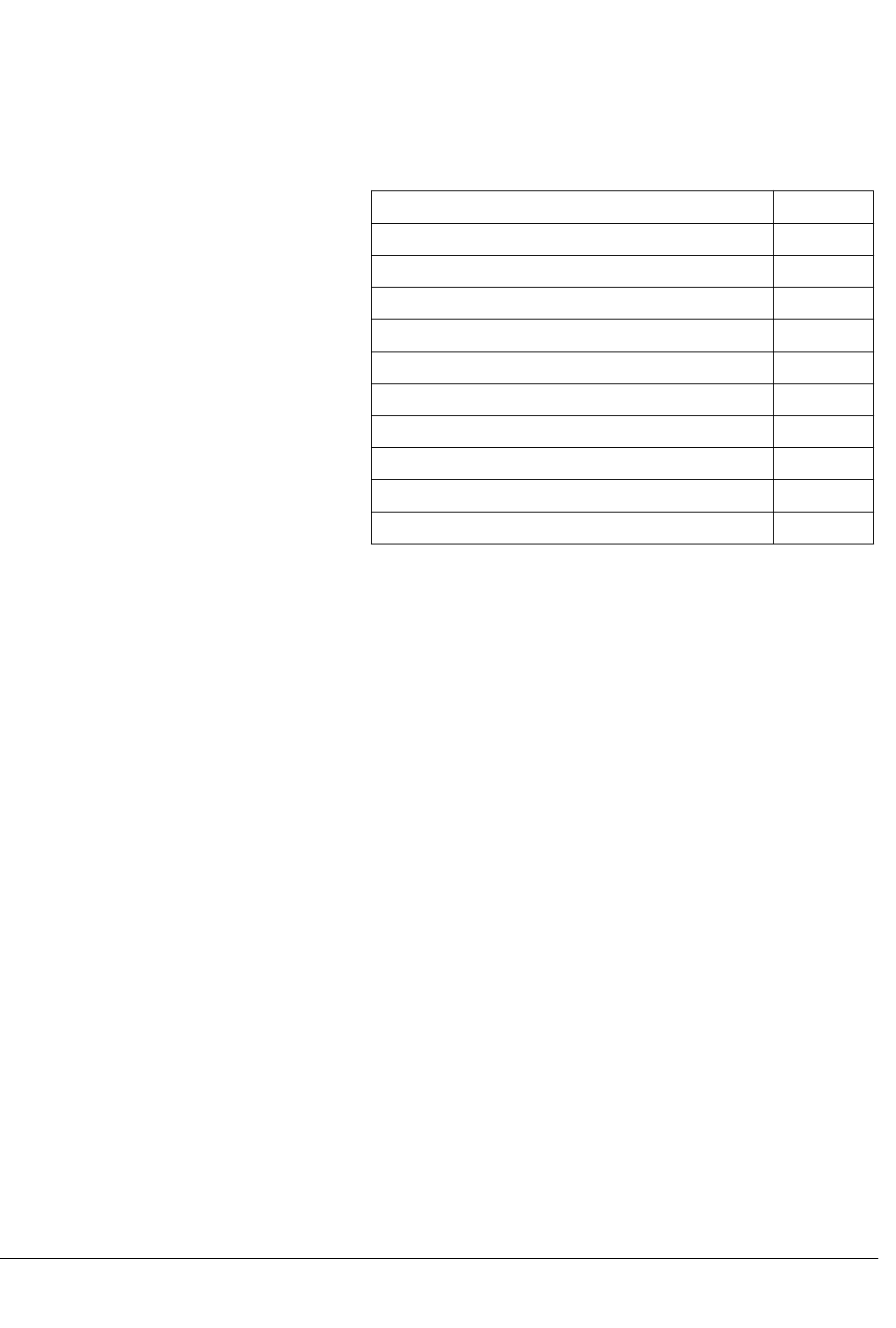

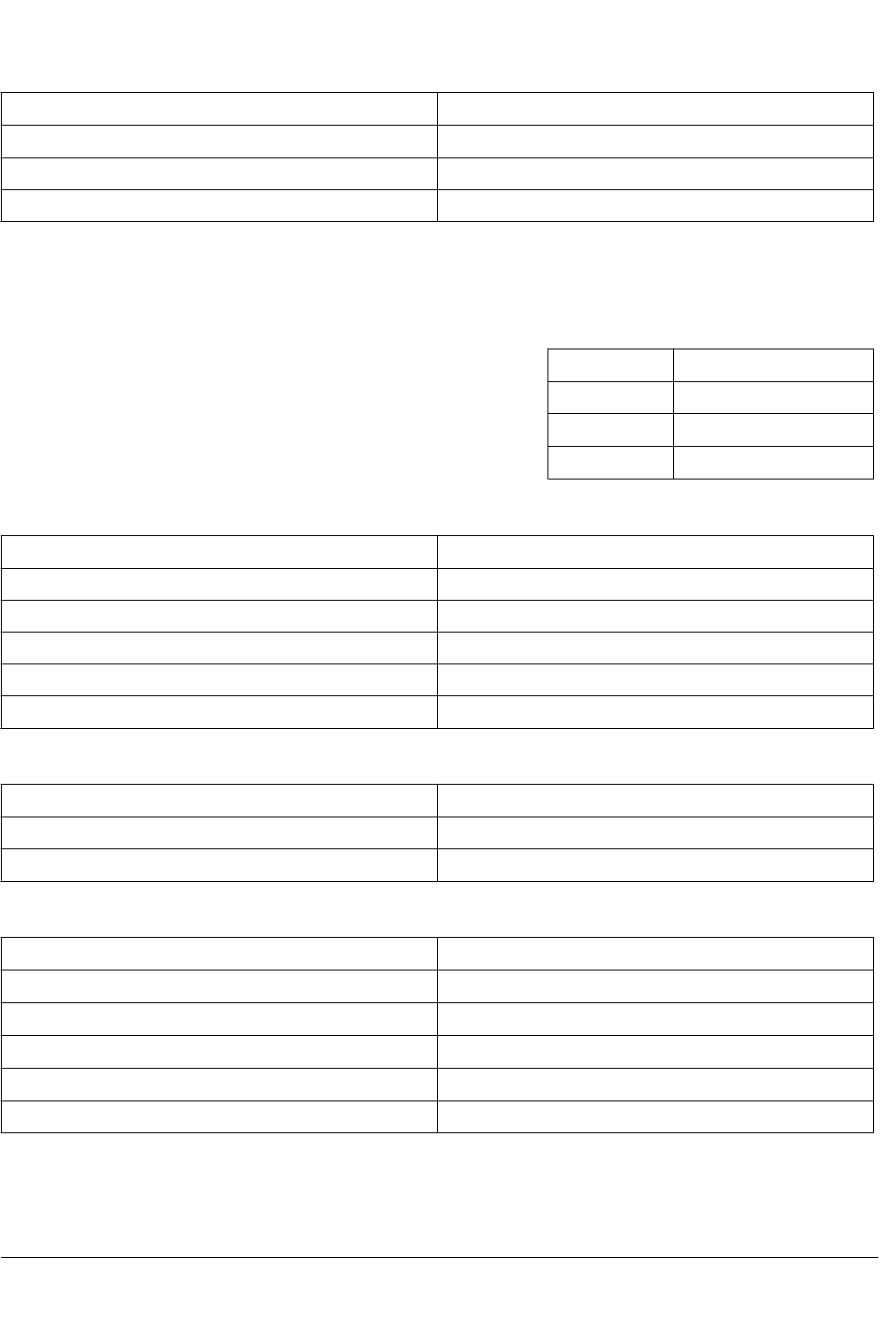

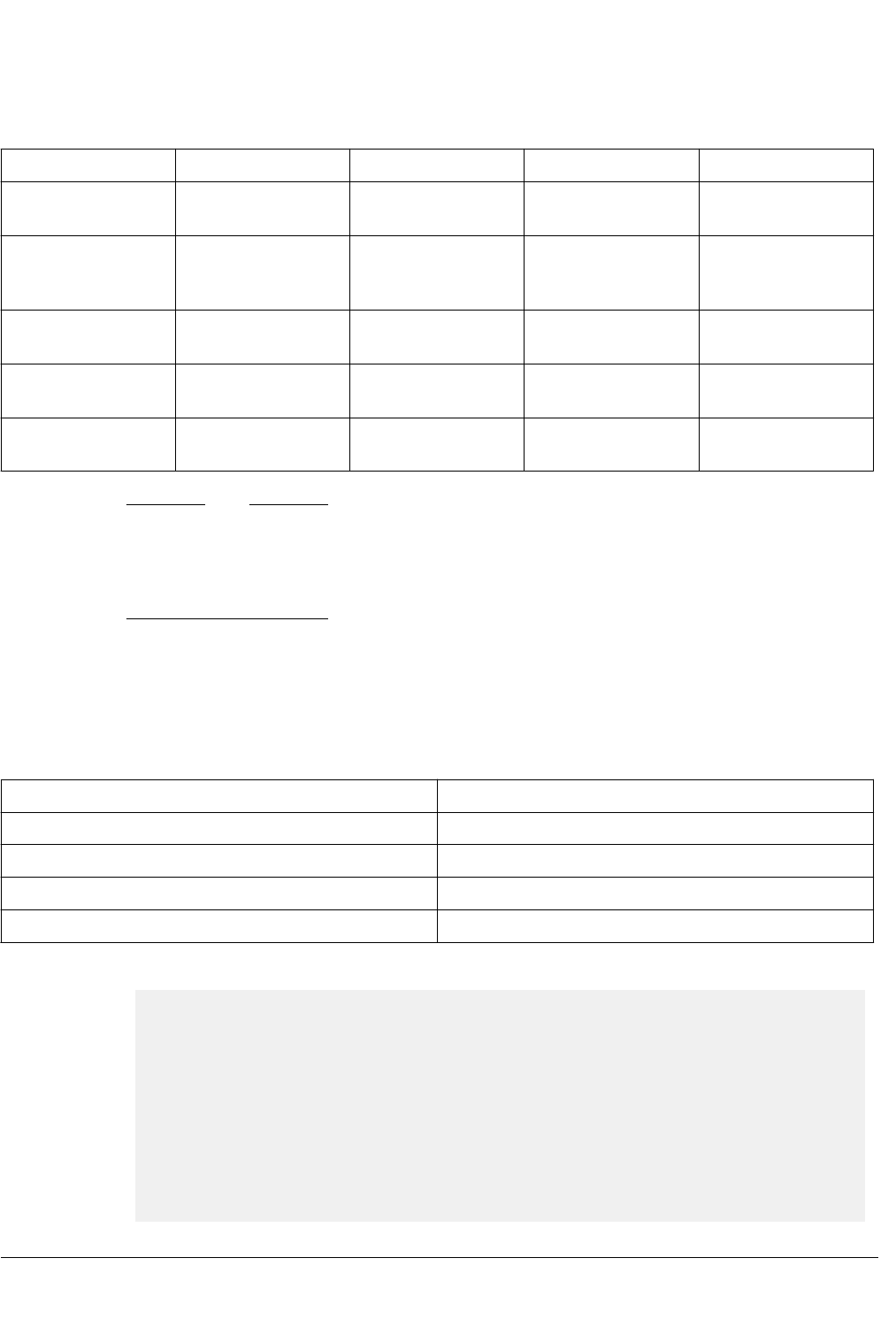

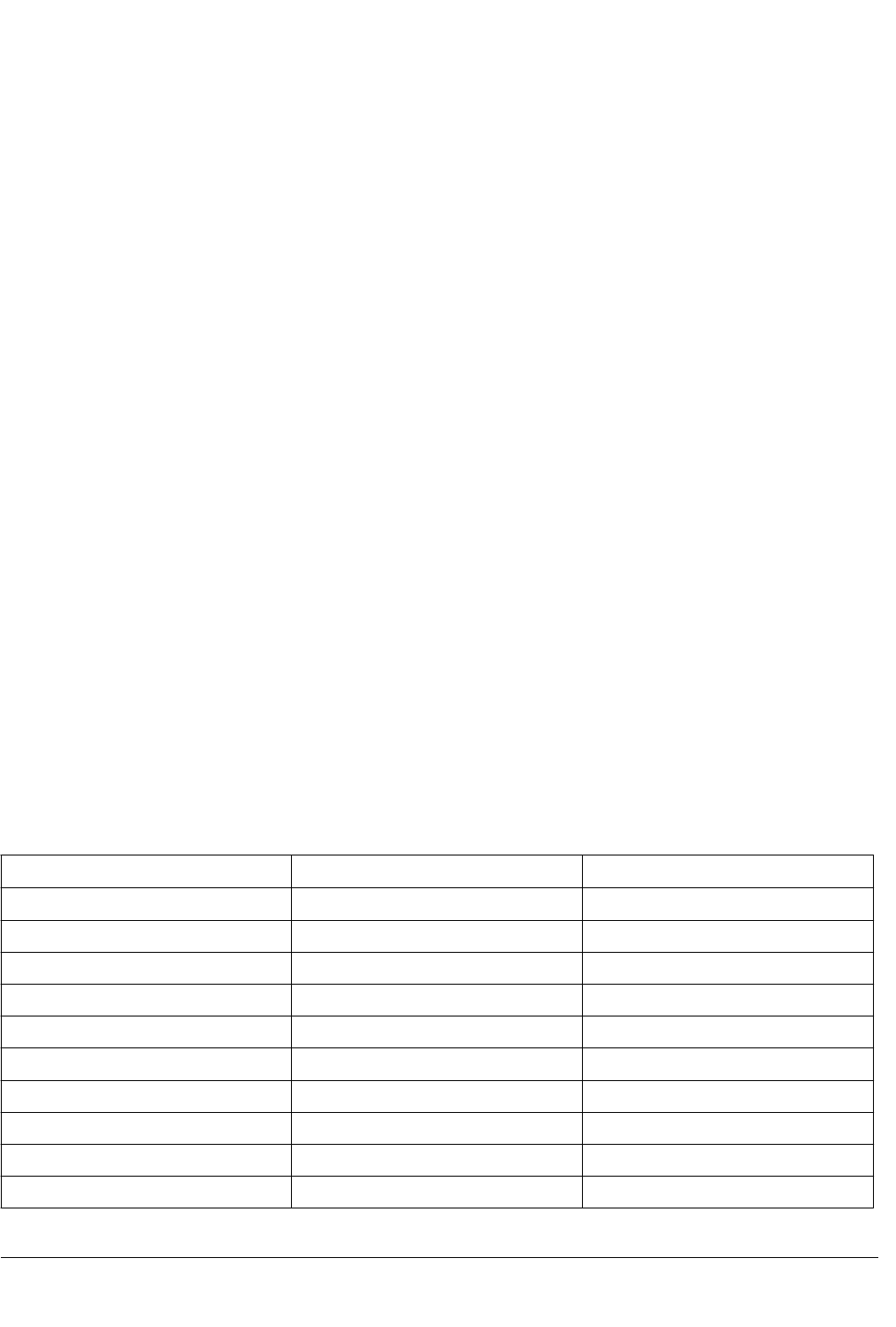

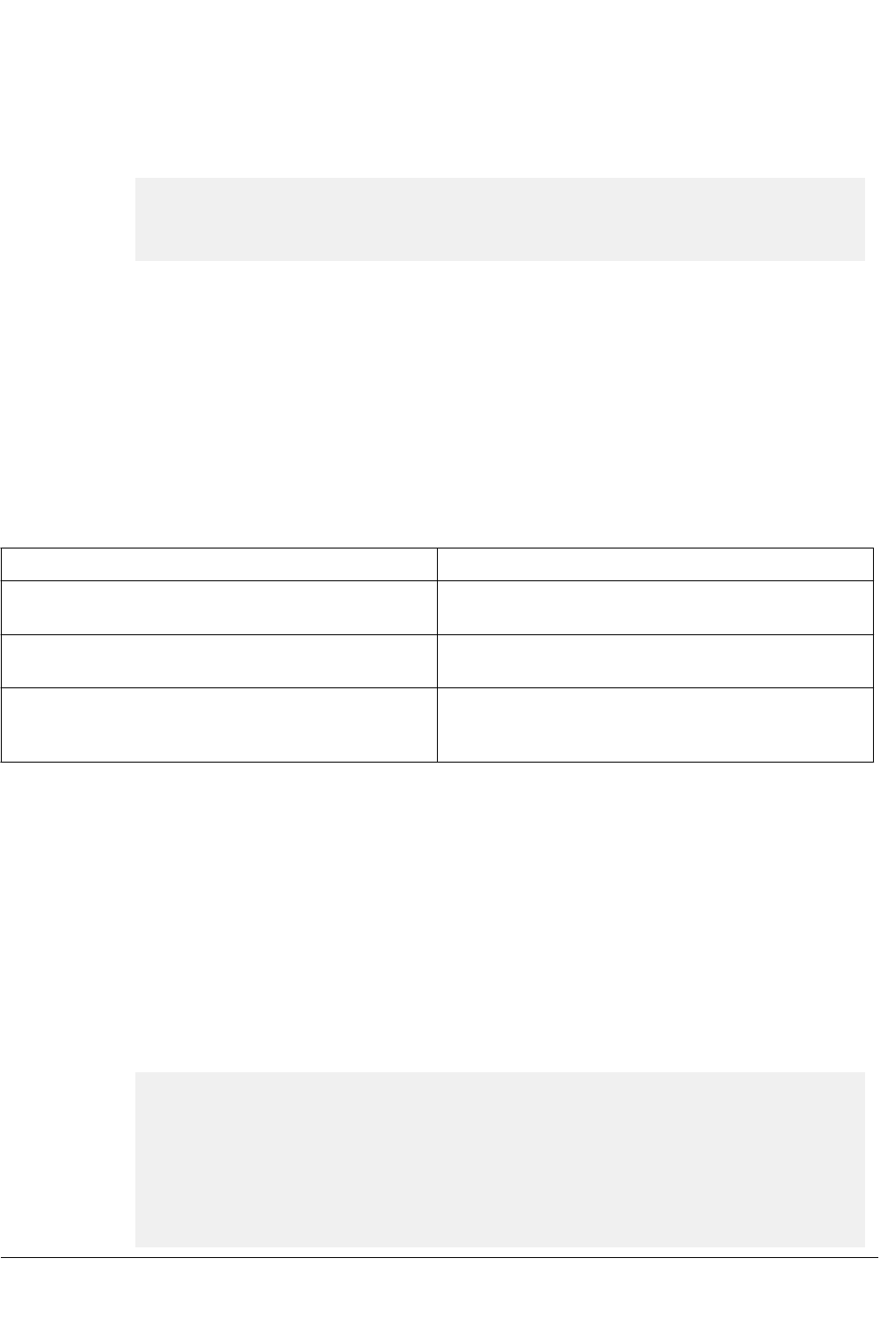

Issue Date Confidentiality Change

A 14 March 2014 Non-Confidential Arm Compiler v6.00 Release

B 15 December 2014 Non-Confidential Arm Compiler v6.01 Release

C 30 June 2015 Non-Confidential Arm Compiler v6.02 Release

D 18 November 2015 Non-Confidential Arm Compiler v6.3 Release

E 24 February 2016 Non-Confidential Arm Compiler v6.4 Release

F 29 June 2016 Non-Confidential Arm Compiler v6.5 Release

G 04 November 2016 Non-Confidential Arm Compiler v6.6 Release

H 08 May 2017 Non-Confidential Arm Compiler v6.6.1 Release

I 29 November 2017 Non-Confidential Arm Compiler v6.6.2 Release

J 28 August 2019 Non-Confidential Arm Compiler v6.6.3 Release

K 26 August 2020 Non-Confidential Arm Compiler v6.6.4 Release

Non-Confidential Proprietary Notice

This document is protected by copyright and other related rights and the practice or implementation of the information contained in

this document may be protected by one or more patents or pending patent applications. No part of this document may be

reproduced in any form by any means without the express prior written permission of Arm. No license, express or implied, by

estoppel or otherwise to any intellectual property rights is granted by this document unless specifically stated.

Your access to the information in this document is conditional upon your acceptance that you will not use or permit others to use

the information for the purposes of determining whether implementations infringe any third party patents.

THIS DOCUMENT IS PROVIDED “AS IS”. ARM PROVIDES NO REPRESENTATIONS AND NO WARRANTIES,

EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF

MERCHANTABILITY, SATISFACTORY QUALITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE

WITH RESPECT TO THE DOCUMENT. For the avoidance of doubt, Arm makes no representation with respect to, and has

undertaken no analysis to identify or understand the scope and content of, third party patents, copyrights, trade secrets, or other

rights.

This document may include technical inaccuracies or typographical errors.

TO THE EXTENT NOT PROHIBITED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY DAMAGES,

INCLUDING WITHOUT LIMITATION ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, PUNITIVE, OR

CONSEQUENTIAL DAMAGES, HOWEVER CAUSED AND REGARDLESS OF THE THEORY OF LIABILITY, ARISING

OUT OF ANY USE OF THIS DOCUMENT, EVEN IF ARM HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH

DAMAGES.

This document consists solely of commercial items. You shall be responsible for ensuring that any use, duplication or disclosure of

this document complies fully with any relevant export laws and regulations to assure that this document or any portion thereof is

not exported, directly or indirectly, in violation of such export laws. Use of the word “partner” in reference to Arm’s customers is

not intended to create or refer to any partnership relationship with any other company. Arm may make changes to this document at

any time and without notice.

If any of the provisions contained in these terms conflict with any of the provisions of any click through or signed written

agreement covering this document with Arm, then the click through or signed written agreement prevails over and supersedes the

conflicting provisions of these terms. This document may be translated into other languages for convenience, and you agree that if

Arm

®

Compiler

DUI0774K Copyright © 2014–2017, 2019, 2020 Arm Limited or its affiliates. All

rights reserved.

2

Non-Confidential

there is any conflict between the English version of this document and any translation, the terms of the English version of the

Agreement shall prevail.

The Arm corporate logo and words marked with

®

or ™ are registered trademarks or trademarks of Arm Limited (or its

subsidiaries) in the US and/or elsewhere. All rights reserved. Other brands and names mentioned in this document may be the

trademarks of their respective owners. Please follow Arm’s trademark usage guidelines at http://www.arm.com/company/policies/

trademarks.

Copyright © 2014–2017, 2019, 2020 Arm Limited (or its affiliates). All rights reserved.

Arm Limited. Company 02557590 registered in England.

110 Fulbourn Road, Cambridge, England CB1 9NJ.

(LES-PRE-20349)

Additional Notices

Some material in this document is based on IEEE 754-1985 IEEE Standard for Binary Floating-Point Arithmetic. The IEEE

disclaims any responsibility or liability resulting from the placement and use in the described manner.

Confidentiality Status

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in

accordance with the terms of the agreement entered into by Arm and the party that Arm delivered this document to.

Unrestricted Access is an Arm internal classification.

Product Status

The information in this document is Final, that is for a developed product.

Web Address

developer.arm.com

Arm

®

Compiler

DUI0774K Copyright © 2014–2017, 2019, 2020 Arm Limited or its affiliates. All

rights reserved.

3

Non-Confidential

Contents

Arm

®

Compiler armclang Reference Guide

Preface

About this book ..................................................... ..................................................... 14

Chapter 1 Compiler Command-line Options

1.1 Support level definitions .......................................................................................... 1-19

1.2 Summary of armclang command-line options ............................ ............................ 1-23

1.3 -c .............................................................................................................................. 1-28

1.4 -D .............................................................. .............................................................. 1-29

1.5 -E .............................................................. .............................................................. 1-30

1.6 -e .............................................................. .............................................................. 1-31

1.7 -fbare-metal-pie ................................................... ................................................... 1-32

1.8 -fbracket-depth=N .................................................................................................... 1-33

1.9 -fcommon, -fno-common ............................................ ............................................ 1-34

1.10 -fdata-sections, -fno-data-sections .......................................................................... 1-35

1.11 -ffast-math, -fno-fast-math ........................................... ........................................... 1-36

1.12 -ffp-mode ........................................................ ........................................................ 1-37

1.13 -ffunction-sections, -fno-function-sections ............................... ............................... 1-39

1.14 @file ........................................................................................................................ 1-40

1.15 -fldm-stm, -fno-ldm-stm ............................................. ............................................. 1-41

1.16 -fno-builtin ................................................................................................................ 1-42

1.17 -fno-inline-functions ................................................ ................................................ 1-44

1.18 -flto, -fno-lto ...................................................... ...................................................... 1-45

1.19 -fexceptions, -fno-exceptions ......................................... ......................................... 1-46

DUI0774K Copyright © 2014–2017, 2019, 2020 Arm Limited or its affiliates. All

rights reserved.

4

Non-Confidential

1.20 -fomit-frame-pointer, -fno-omit-frame-pointer .......................................................... 1-47

1.21 -fropi, -fno-ropi .................................................... .................................................... 1-48

1.22 -fropi-lowering, -fno-ropi-lowering ............................................................................ 1-49

1.23 -frwpi, -fno-rwpi ................................................... ................................................... 1-50

1.24 -frwpi-lowering, -fno-rwpi-lowering .......................................................................... 1-51

1.25 -fshort-enums, -fno-short-enums ...................................... ...................................... 1-52

1.26 -fshort-wchar, -fno-short-wchar ................................................................................ 1-54

1.27 -fstack-protector, -fstack-protector-all, -fstack-protector-strong, -fno-stack-protector ....

.................................................................................................................................. 1-55

1.28 -fstrict-aliasing, -fno-strict-aliasing ..................................... ..................................... 1-57

1.29 -fvectorize, -fno-vectorize ........................................................................................ 1-58

1.30 -ftrapv ...................................................................................................................... 1-59

1.31 -fwrapv .......................................................... .......................................................... 1-60

1.32 -g, -gdwarf-2, -gdwarf-3, -gdwarf-4 .................................... .................................... 1-61

1.33 -I .............................................................................................................................. 1-62

1.34 -include .................................................................................................................... 1-63

1.35 -L .............................................................. .............................................................. 1-64

1.36 -l ............................................................... ............................................................... 1-65

1.37 -M, -MM ......................................................... ......................................................... 1-66

1.38 -MD, -MMD .............................................................................................................. 1-67

1.39 -MF .......................................................................................................................... 1-68

1.40 -MG .......................................................................................................................... 1-69

1.41 -MP .......................................................................................................................... 1-70

1.42 -MT .......................................................................................................................... 1-71

1.43 -march .......................................................... .......................................................... 1-72

1.44 -marm ...................................................................................................................... 1-74

1.45 -mbig-endian ............................................................................................................ 1-75

1.46 -mcmse .................................................................................................................... 1-76

1.47 -mcpu ........................................................... ........................................................... 1-78

1.48 -mexecute-only ........................................................................................................ 1-82

1.49 -mfloat-abi ................................................................................................................ 1-83

1.50 -mfpu ........................................................... ........................................................... 1-84

1.51 -mimplicit-it ....................................................... ....................................................... 1-86

1.52 -mlittle-endian .......................................................................................................... 1-87

1.53 -munaligned-access, -mno-unaligned-access ............................ ............................ 1-88

1.54 -mthumb .................................................................................................................. 1-89

1.55 -nostdlib ......................................................... ......................................................... 1-90

1.56 -nostdlibinc .............................................................................................................. 1-91

1.57 -o .............................................................. .............................................................. 1-92

1.58 -O .............................................................. .............................................................. 1-93

1.59 -pedantic .................................................................................................................. 1-95

1.60 -pedantic-errors ................................................... ................................................... 1-96

1.61 -Rpass .......................................................... .......................................................... 1-97

1.62 -S .............................................................. .............................................................. 1-99

1.63 -save-temps ..................................................... ..................................................... 1-100

1.64 -std ............................................................ ............................................................ 1-101

1.65 --target ......................................................... ......................................................... 1-103

1.66 -U ............................................................. ............................................................. 1-104

1.67 -u ............................................................. ............................................................. 1-105

1.68 -v ............................................................................................................................ 1-106

DUI0774K Copyright © 2014–2017, 2019, 2020 Arm Limited or its affiliates. All

rights reserved.

5

Non-Confidential

1.69 --version ........................................................ ........................................................ 1-107

1.70 --version_number ................................................. ................................................. 1-108

1.71 --vsn ........................................................... ........................................................... 1-109

1.72 -W .......................................................................................................................... 1-110

1.73 -Wl .......................................................................................................................... 1-111

1.74 -Xlinker ......................................................... ......................................................... 1-112

1.75 -x ............................................................................................................................ 1-113

1.76 -### ........................................................................................................................ 1-114

Chapter 2 Compiler-specific Keywords and Operators

2.1 Compiler-specific keywords and operators ............................................................ 2-116

2.2 __alignof__ ............................................................................................................ 2-117

2.3 __asm .................................................................................................................... 2-119

2.4 __declspec attributes .............................................. .............................................. 2-121

2.5 __declspec(noinline) .............................................................................................. 2-122

2.6 __declspec(noreturn) .............................................. .............................................. 2-123

2.7 __declspec(nothrow) .............................................. .............................................. 2-124

2.8 __inline .................................................................................................................. 2-125

2.9 __unaligned ..................................................... ..................................................... 2-126

2.10 __promise .............................................................................................................. 2-127

Chapter 3 Compiler-specific Function, Variable, and Type Attributes

3.1 Function attributes ................................................ ................................................ 3-130

3.2 __attribute__((always_inline)) function attribute .................................................... 3-132

3.3 __attribute__((cmse_nonsecure_call)) function attribute ................... ................... 3-133

3.4 __attribute__((cmse_nonsecure_entry)) function attribute .................................... 3-134

3.5 __attribute__((const)) function attribute ................................ ................................ 3-135

3.6 __attribute__((constructor(priority))) function attribute .......................................... 3-136

3.7 __attribute__((format_arg(string-index))) function attribute ................. ................. 3-137

3.8 __attribute__((interrupt("type"))) function attribute ................................................ 3-138

3.9 __attribute__((malloc)) function attribute ............................... ............................... 3-139

3.10 __attribute__((naked)) function attribute ............................... ............................... 3-140

3.11 __attribute__((noinline)) function attribute .............................. .............................. 3-141

3.12 __attribute__((nonnull)) function attribute .............................................................. 3-142

3.13 __attribute__((noreturn)) function attribute ............................................................ 3-143

3.14 __attribute__((nothrow)) function attribute .............................. .............................. 3-144

3.15 __attribute__((pcs("calling_convention"))) function attribute ................ ................ 3-145

3.16 __attribute__((pure)) function attribute .................................................................. 3-146

3.17 __attribute__((section("name"))) function attribute ................................................ 3-147

3.18 __attribute__((used)) function attribute ................................ ................................ 3-148

3.19 __attribute__((unused)) function attribute .............................. .............................. 3-149

3.20 __attribute__((value_in_regs)) function attribute ......................... ......................... 3-150

3.21 __attribute__((visibility("visibility_type"))) function attribute ................. ................. 3-151

3.22 __attribute__((weak)) function attribute ................................ ................................ 3-152

3.23 __attribute__((weakref("target"))) function attribute ....................... ....................... 3-153

3.24 Type attributes ................................................... ................................................... 3-154

3.25 __attribute__((aligned)) type attribute ................................. ................................. 3-155

3.26 __attribute__((packed)) type attribute ................................. ................................. 3-156

3.27 __attribute__((transparent_union)) type attribute .................................................. 3-157

3.28 Variable attributes .................................................................................................. 3-158

DUI0774K Copyright © 2014–2017, 2019, 2020 Arm Limited or its affiliates. All

rights reserved.

6

Non-Confidential

3.29 __attribute__((alias)) variable attribute .................................................................. 3-159

3.30 __attribute__((aligned)) variable attribute .............................................................. 3-160

3.31 __attribute__((deprecated)) variable attribute ........................... ........................... 3-161

3.32 __attribute__((packed)) variable attribute .............................................................. 3-162

3.33 __attribute__((section("name"))) variable attribute ................................................ 3-163

3.34 __attribute__((used)) variable attribute ................................ ................................ 3-164

3.35 __attribute__((unused)) variable attribute .............................. .............................. 3-165

3.36 __attribute__((weak)) variable attribute ................................ ................................ 3-166

3.37 __attribute__((weakref("target"))) variable attribute ....................... ....................... 3-167

Chapter 4 Compiler-specific Intrinsics

4.1 __breakpoint intrinsic .............................................. .............................................. 4-169

4.2 __current_pc intrinsic ............................................................................................ 4-170

4.3 __current_sp intrinsic ............................................................................................ 4-171

4.4 __disable_fiq intrinsic ............................................................................................ 4-172

4.5 __disable_irq intrinsic ............................................................................................ 4-173

4.6 __enable_fiq intrinsic .............................................. .............................................. 4-174

4.7 __enable_irq intrinsic .............................................. .............................................. 4-175

4.8 __force_stores intrinsic .......................................................................................... 4-176

4.9 __memory_changed intrinsic ........................................ ........................................ 4-177

4.10 __schedule_barrier intrinsic ......................................... ......................................... 4-178

4.11 __semihost intrinsic ............................................... ............................................... 4-179

4.12 __vfp_status intrinsic .............................................. .............................................. 4-181

Chapter 5 Compiler-specific Pragmas

5.1 #pragma clang system_header ...................................... ...................................... 5-183

5.2 #pragma clang diagnostic ...................................................................................... 5-184

5.3 #pragma clang section .......................................................................................... 5-186

5.4 #pragma once ........................................................................................................ 5-188

5.5 #pragma pack(...) .................................................................................................. 5-189

5.6 #pragma unroll[(n)], #pragma unroll_completely ......................... ......................... 5-191

5.7 #pragma weak symbol, #pragma weak symbol1 = symbol2 ................ ................ 5-192

Chapter 6 Other Compiler-specific Features

6.1 ACLE support ........................................................................................................ 6-194

6.2 Predefined macros ................................................................................................ 6-195

6.3 Inline functions ................................................... ................................................... 6-200

6.4 Volatile variables .................................................................................................... 6-201

6.5 Half-precision floating-point number format ............................. ............................. 6-202

6.6 TT instruction intrinsics .......................................................................................... 6-203

6.7 Non-secure function pointer intrinsics ................................. ................................. 6-206

Chapter 7 Standard C Implementation Definition

7.1 Implementation definition ........................................... ........................................... 7-208

7.2 Translation ...................................................... ...................................................... 7-209

7.3 Translation limits .................................................................................................... 7-210

7.4 Environment .......................................................................................................... 7-212

7.5 Identifiers ....................................................... ....................................................... 7-214

7.6 Characters ...................................................... ...................................................... 7-215

7.7 Integers .................................................................................................................. 7-217

7.8 Floating-point .................................................... .................................................... 7-218

DUI0774K Copyright © 2014–2017, 2019, 2020 Arm Limited or its affiliates. All

rights reserved.

7

Non-Confidential

7.9 Arrays and pointers ............................................... ............................................... 7-219

7.10 Hints ...................................................................................................................... 7-220

7.11 Structures, unions, enumerations, and bitfields .......................... .......................... 7-221

7.12 Qualifiers ....................................................... ....................................................... 7-222

7.13 Preprocessing directives ........................................... ........................................... 7-223

7.14 Library functions .................................................................................................... 7-225

7.15 Architecture ..................................................... ..................................................... 7-230

Chapter 8 Standard C++ Implementation Definition

8.1 Implementation definition ........................................... ........................................... 8-237

8.2 General .................................................................................................................. 8-238

8.3 Lexical conventions ............................................... ............................................... 8-239

8.4 Basic concepts ...................................................................................................... 8-240

8.5 Standard conversions ............................................................................................ 8-241

8.6 Expressions ..................................................... ..................................................... 8-242

8.7 Declarations ..................................................... ..................................................... 8-244

8.8 Declarators ............................................................................................................ 8-245

8.9 Templates .............................................................................................................. 8-246

8.10 Exception handling ................................................................................................ 8-247

8.11 Preprocessing directives ........................................... ........................................... 8-248

8.12 Library introduction ................................................................................................ 8-249

8.13 Language support library ........................................... ........................................... 8-250

8.14 General utilities library ............................................. ............................................. 8-251

8.15 Strings library .................................................... .................................................... 8-252

8.16 Localization library ................................................ ................................................ 8-253

8.17 Containers library .................................................................................................. 8-254

8.18 Input/output library ................................................ ................................................ 8-255

8.19 Regular expressions library ......................................... ......................................... 8-256

8.20 Atomic operations library ........................................... ........................................... 8-257

8.21 Thread support library ............................................. ............................................. 8-258

8.22 Implementation quantities ...................................................................................... 8-259

Chapter 9 armclang Integrated Assembler

9.1 Syntax of assembly files for integrated assembler ................................................ 9-263

9.2 Assembly expressions ............................................. ............................................. 9-265

9.3 Alignment directives ............................................... ............................................... 9-270

9.4 Data definition directives ........................................... ........................................... 9-272

9.5 String definition directives ...................................................................................... 9-275

9.6 Floating-point data definition directives ................................ ................................ 9-277

9.7 Section directives .................................................................................................. 9-278

9.8 Conditional assembly directives ............................................................................ 9-283

9.9 Macro directives .................................................................................................... 9-285

9.10 Symbol binding directives ...................................................................................... 9-287

9.11 Org directive .......................................................................................................... 9-289

9.12 AArch32 Target selection directives ................................... ................................... 9-290

9.13 AArch64 Target selection directives ................................... ................................... 9-292

9.14 Space-filling directives ............................................. ............................................. 9-293

9.15 Type directive .................................................... .................................................... 9-294

DUI0774K Copyright © 2014–2017, 2019, 2020 Arm Limited or its affiliates. All

rights reserved.

8

Non-Confidential

Chapter 10 armclang Inline Assembler

10.1 Inline Assembly ................................................. ................................................. 10-296

10.2 File-scope inline assembly ......................................... ......................................... 10-297

10.3 Inline assembly statements within a function ........................... ........................... 10-298

10.4 Inline assembly constraint strings ........................................................................ 10-302

10.5 Inline assembly template modifiers .................................. .................................. 10-307

10.6 Forcing inline assembly operands into specific registers .................. .................. 10-310

10.7 Symbol references and branches into and out of inline assembly ........... ........... 10-311

10.8 Duplication of labels in inline assembly statements ...................... ...................... 10-312

Appendix A armclang Reference Guide Changes

A.1 Changes for the armclang Reference Guide ....................... ....................... Appx-A-314

DUI0774K Copyright © 2014–2017, 2019, 2020 Arm Limited or its affiliates. All

rights reserved.

9

Non-Confidential

List of Figures

Arm

®

Compiler armclang Reference Guide

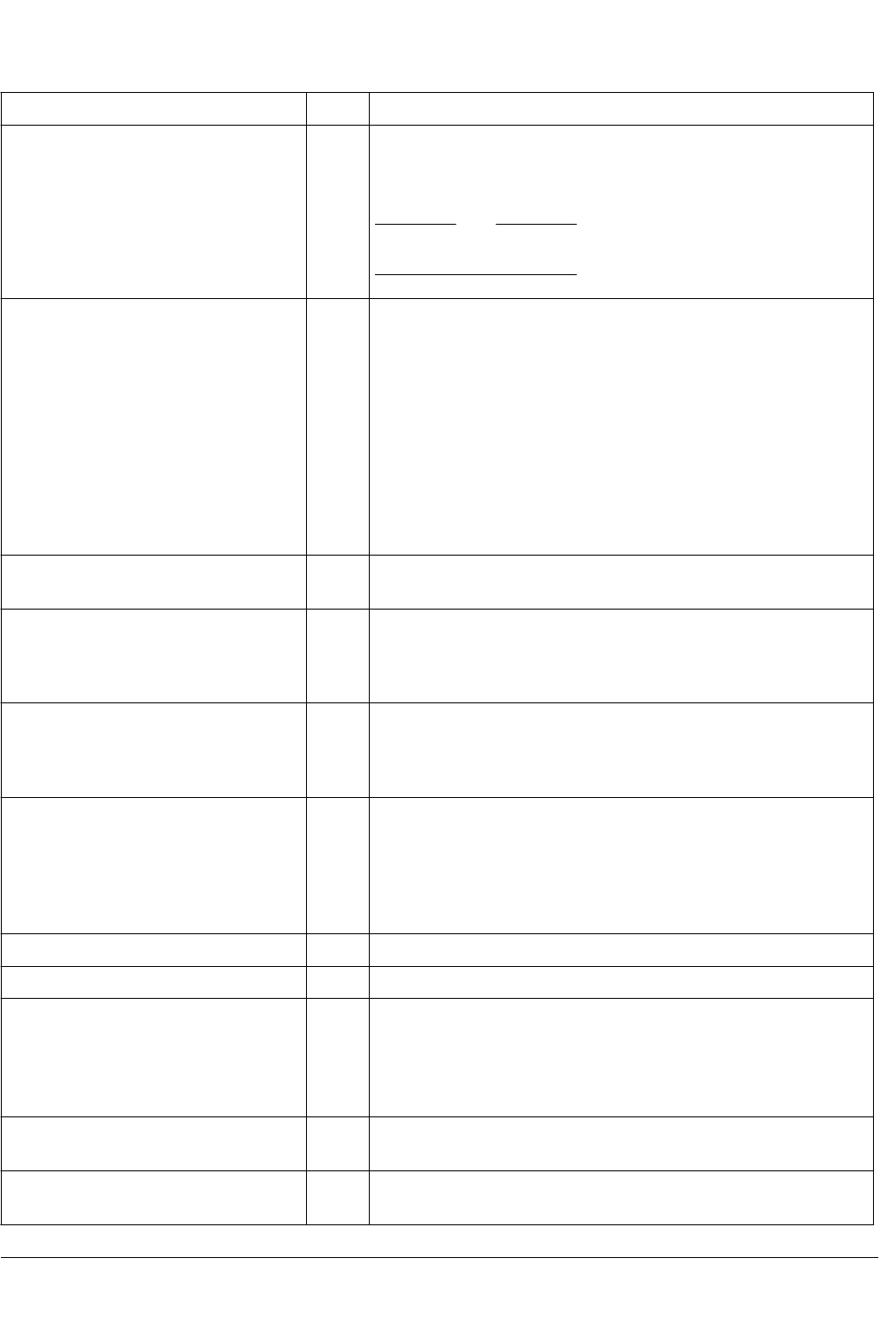

Figure 1-1 Integration boundaries in Arm Compiler 6. ............................................................................ 1-21

Figure 5-1 Nonpacked structure S ........................................................................................................ 5-190

Figure 5-2 Packed structure SP ............................................................................................................ 5-190

Figure 6-1 IEEE half-precision floating-point format ............................................................................. 6-202

DUI0774K Copyright © 2014–2017, 2019, 2020 Arm Limited or its affiliates. All

rights reserved.

10

Non-Confidential

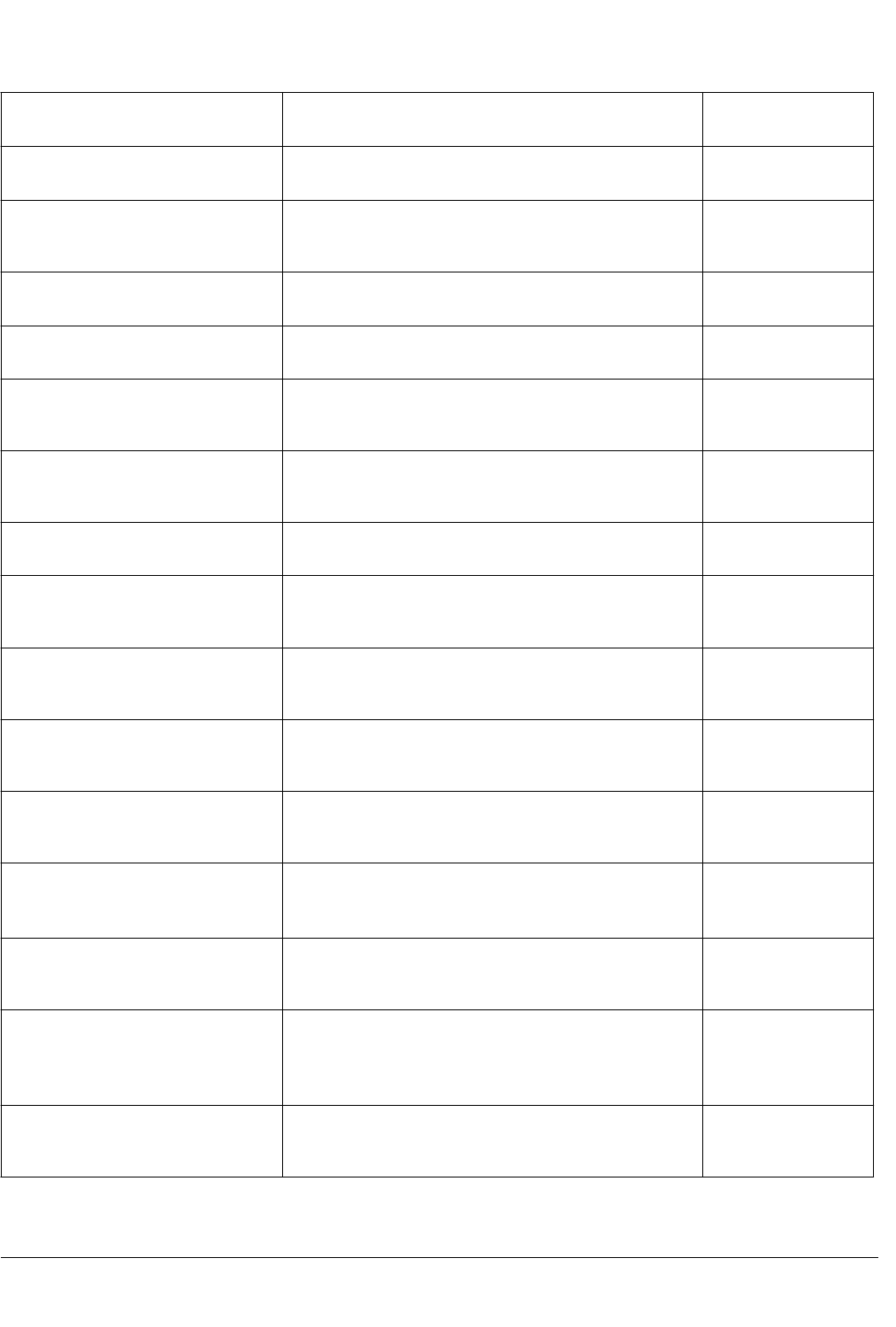

List of Tables

Arm

®

Compiler armclang Reference Guide

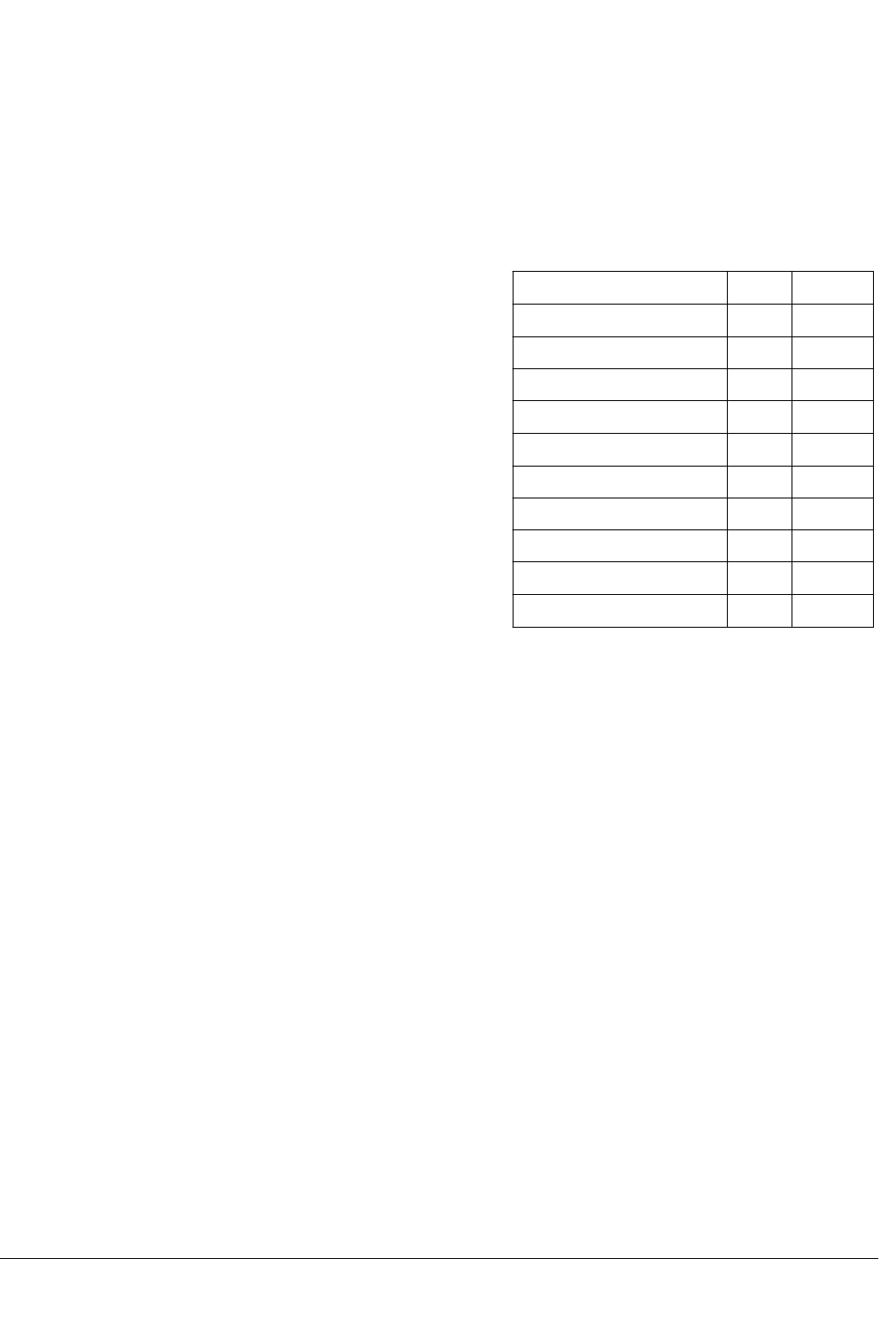

Table 1-1 armclang command-line options ............................................................................................ 1-23

Table 1-2 Floating-point library variants ................................................................................................ 1-36

Table 1-3 Floating-point library variant selection ................................................................................... 1-38

Table 1-4 Compiling without the -o option ............................................................................................. 1-92

Table 3-1 Function attributes that the compiler supports, and their equivalents ................................. 3-130

Table 4-1 Modifying the FPSCR flags ................................................................................................. 4-181

Table 6-1 Predefined macros .............................................................................................................. 6-195

Table 7-1 Translation limits .................................................................................................................. 7-210

Table 9-1 Modifiers .............................................................................................................................. 9-265

Table 9-2 Unary operators ................................................................................................................... 9-266

Table 9-3 Binary operators .................................................................................................................. 9-266

Table 9-4 Binary logical operators ....................................................................................................... 9-266

Table 9-5 Binary bitwise operators ...................................................................................................... 9-266

Table 9-6 Binary comparison operators ............................................................................................... 9-267

Table 9-7 Relocation specifiers for AArch32 state ............................................................................... 9-267

Table 9-8 Relocation specifiers for AArch64 state ............................................................................... 9-268

Table 9-9 Data definition directives ..................................................................................................... 9-272

Table 9-10 Expression types supported by the data definition directives .............................................. 9-273

Table 9-11 Aliases for the data definition directives .............................................................................. 9-273

Table 9-12 Escape characters for the string definition directives .......................................................... 9-275

Table 9-13 Aliases for the floating-point data definition directives ......................................................... 9-277

Table 9-14 Section flags ........................................................................................................................ 9-279

Table 9-15 Section Type ........................................................................................................................ 9-280

DUI0774K Copyright © 2014–2017, 2019, 2020 Arm Limited or its affiliates. All

rights reserved.

11

Non-Confidential

Table 9-16 Sections with implicit flags and default types ...................................................................... 9-281

Table 9-17 .if condition modifiers ........................................................................................................... 9-283

Table 9-18 Macro parameter qualifier .................................................................................................... 9-285

Table 10-1 Constraint modifiers ........................................................................................................... 10-302

Table A-1 Changes between 6.6.4 (revision K) and 6.6.3 (revision J) ....................................... Appx-A-314

DUI0774K Copyright © 2014–2017, 2019, 2020 Arm Limited or its affiliates. All

rights reserved.

12

Non-Confidential

About this book

The Arm

®

Compiler armclang Reference Guide provides user information for the Arm compiler,

armclang. armclang is an optimizing C and C++ compiler that compiles Standard C and Standard C++

source code into machine code for Arm architecture-based processors.

Using this book

This book is organized into the following chapters:

Chapter 1 Compiler Command-line Options

This chapter summarizes the supported options used with armclang.

Chapter 2 Compiler-specific Keywords and Operators

Summarizes the compiler-specific keywords and operators that are extensions to the C and C++

Standards.

Chapter 3 Compiler-specific Function, Variable, and Type Attributes

Summarizes the compiler-specific function, variable, and type attributes that are extensions to the

C and C++ Standards.

Chapter 4 Compiler-specific Intrinsics

Summarizes the Arm compiler-specific intrinsics that are extensions to the C and C++ Standards.

Chapter 5 Compiler-specific Pragmas

Summarizes the Arm compiler-specific pragmas that are extensions to the C and C++ Standards.

Chapter 6 Other Compiler-specific Features

Summarizes compiler-specific features that are extensions to the C and C++ Standards, such as

predefined macros.

Chapter 7 Standard C Implementation Definition

Provides information required by the ISO C standard for conforming C implementations.

Chapter 8 Standard C++ Implementation Definition

Provides information required by the ISO C++ Standard for conforming C++ implementations.

Chapter 9 armclang Integrated Assembler

Provides information on integrated assembler features, such as the directives you can use when

writing assembly language source files in the armclang integrated assembler syntax.

Chapter 10 armclang Inline Assembler

Provides reference information on writing inline assembly.

Appendix A armclang Reference Guide Changes

Describes the technical changes that have been made to the armclang Reference Guide.

Glossary

The Arm

®

Glossary is a list of terms used in Arm documentation, together with definitions for those

terms. The Arm Glossary does not contain terms that are industry standard unless the Arm meaning

differs from the generally accepted meaning.

See the Arm

®

Glossary for more information.

Typographic conventions

italic

Introduces special terminology, denotes cross-references, and citations.

bold

Highlights interface elements, such as menu names. Denotes signal names. Also used for terms

in descriptive lists, where appropriate.

Preface

About this book

DUI0774K Copyright © 2014–2017, 2019, 2020 Arm Limited or its affiliates. All

rights reserved.

14

Non-Confidential

monospace

Denotes text that you can enter at the keyboard, such as commands, file and program names,

and source code.

monospace

Denotes a permitted abbreviation for a command or option. You can enter the underlined text

instead of the full command or option name.

monospace italic

Denotes arguments to monospace text where the argument is to be replaced by a specific value.

monospace bold

Denotes language keywords when used outside example code.

<and>

Encloses replaceable terms for assembler syntax where they appear in code or code fragments.

For example:

MRC p15, 0, <Rd>, <CRn>, <CRm>, <Opcode_2>

SMALL CAPITALS

Used in body text for a few terms that have specific technical meanings, that are defined in the

Arm

®

Glossary. For example, IMPLEMENTATION DEFINED, IMPLEMENTATION SPECIFIC, UNKNOWN, and

UNPREDICTABLE.

Feedback

Feedback on this product

If you have any comments or suggestions about this product, contact your supplier and give:

• The product name.

• The product revision or version.

• An explanation with as much information as you can provide. Include symptoms and diagnostic

procedures if appropriate.

Feedback on content

If you have comments on content then send an e-mail to [email protected]. Give:

• The title Arm Compiler armclang Reference Guide.

• The number DUI0774K.

• If applicable, the page number(s) to which your comments refer.

• A concise explanation of your comments.

Arm also welcomes general suggestions for additions and improvements.

Note

Arm tests the PDF only in Adobe Acrobat and Acrobat Reader, and cannot guarantee the quality of the

represented document when used with any other PDF reader.

Other information

• Arm

®

Developer.

• Arm

®

Information Center.

• Arm

®

Technical Support Knowledge Articles.

• Technical Support.

• Arm

®

Glossary.

Preface

About this book

DUI0774K Copyright © 2014–2017, 2019, 2020 Arm Limited or its affiliates. All

rights reserved.

15

Non-Confidential

Chapter 1

Compiler Command-line Options

This chapter summarizes the supported options used with armclang.

armclang provides many command-line options, including most Clang command-line options in addition

to a number of Arm-specific options. Additional information about community feature command-line

options is available in the Clang and LLVM documentation on the LLVM Compiler Infrastructure

Project web site, http://llvm.org.

Note

Be aware of the following:

• Generated code might be different between two Arm Compiler releases.

• For a feature release, there might be significant code generation differences.

It contains the following sections:

• 1.1 Support level definitions on page 1-19.

• 1.2 Summary of armclang command-line options on page 1-23.

• 1.3 -c on page 1-28.

• 1.4 -D on page 1-29.

• 1.5 -E on page 1-30.

• 1.6 -e on page 1-31.

• 1.7 -fbare-metal-pie on page 1-32.

• 1.8 -fbracket-depth=N on page 1-33.

• 1.9 -fcommon, -fno-common on page 1-34.

• 1.10 -fdata-sections, -fno-data-sections on page 1-35.

• 1.11 -ffast-math, -fno-fast-math on page 1-36.

• 1.12 -ffp-mode on page 1-37.

• 1.13 -ffunction-sections, -fno-function-sections on page 1-39.

DUI0774K

Copyright © 2014–2017, 2019, 2020 Arm Limited or its affiliates. All

rights reserved.

1-16

Non-Confidential

• 1.14 @file on page 1-40.

• 1.15 -fldm-stm, -fno-ldm-stm on page 1-41.

• 1.16 -fno-builtin on page 1-42.

• 1.17 -fno-inline-functions on page 1-44.

• 1.18 -flto, -fno-lto on page 1-45.

• 1.19 -fexceptions, -fno-exceptions on page 1-46.

• 1.20 -fomit-frame-pointer, -fno-omit-frame-pointer on page 1-47.

• 1.21 -fropi, -fno-ropi on page 1-48.

• 1.22 -fropi-lowering, -fno-ropi-lowering on page 1-49.

• 1.23 -frwpi, -fno-rwpi on page 1-50.

• 1.24 -frwpi-lowering, -fno-rwpi-lowering on page 1-51.

• 1.25 -fshort-enums, -fno-short-enums on page 1-52.

• 1.26 -fshort-wchar, -fno-short-wchar on page 1-54.

• 1.27 -fstack-protector, -fstack-protector-all, -fstack-protector-strong, -fno-stack-protector

on page 1-55.

• 1.28 -fstrict-aliasing, -fno-strict-aliasing on page 1-57.

• 1.29 -fvectorize, -fno-vectorize on page 1-58.

• 1.30 -ftrapv on page 1-59.

• 1.31 -fwrapv on page 1-60.

• 1.32 -g, -gdwarf-2, -gdwarf-3, -gdwarf-4 on page 1-61.

• 1.33 -I on page 1-62.

• 1.34 -include on page 1-63.

• 1.35 -L on page 1-64.

• 1.36 -l on page 1-65.

• 1.37 -M, -MM on page 1-66.

• 1.38 -MD, -MMD on page 1-67.

• 1.39 -MF on page 1-68.

• 1.40 -MG on page 1-69.

• 1.41 -MP on page 1-70.

• 1.42 -MT on page 1-71.

• 1.43 -march on page 1-72.

• 1.44 -marm on page 1-74.

• 1.45 -mbig-endian on page 1-75.

• 1.46 -mcmse on page 1-76.

• 1.47 -mcpu on page 1-78.

• 1.48 -mexecute-only on page 1-82.

• 1.49 -mfloat-abi on page 1-83.

• 1.50 -mfpu on page 1-84.

• 1.51 -mimplicit-it on page 1-86.

• 1.52 -mlittle-endian on page 1-87.

• 1.53 -munaligned-access, -mno-unaligned-access on page 1-88.

• 1.54 -mthumb on page 1-89.

• 1.55 -nostdlib on page 1-90.

• 1.56 -nostdlibinc on page 1-91.

• 1.57 -o on page 1-92.

• 1.58 -O on page 1-93.

• 1.59 -pedantic on page 1-95.

• 1.60 -pedantic-errors on page 1-96.

• 1.61 -Rpass on page 1-97.

• 1.62 -S on page 1-99.

• 1.63 -save-temps on page 1-100.

• 1.64 -std on page 1-101.

• 1.65 --target on page 1-103.

• 1.66 -U on page 1-104.

• 1.67 -u on page 1-105.

• 1.68 -v on page 1-106.

1 Compiler Command-line Options

DUI0774K Copyright © 2014–2017, 2019, 2020 Arm Limited or its affiliates. All

rights reserved.

1-17

Non-Confidential

• 1.69 --version on page 1-107.

• 1.70 --version_number on page 1-108.

• 1.71 --vsn on page 1-109.

• 1.72 -W on page 1-110.

• 1.73 -Wl on page 1-111.

• 1.74 -Xlinker on page 1-112.

• 1.75 -x on page 1-113.

• 1.76 -### on page 1-114.

1 Compiler Command-line Options

DUI0774K Copyright © 2014–2017, 2019, 2020 Arm Limited or its affiliates. All

rights reserved.

1-18

Non-Confidential

1.1 Support level definitions

This describes the levels of support for various Arm Compiler 6 features.

Arm Compiler 6 is built on Clang and LLVM technology. Therefore it has more functionality than the set

of product features described in the documentation. The following definitions clarify the levels of

support and guarantees on functionality that are expected from these features.

Arm welcomes feedback regarding the use of all Arm Compiler 6 features, and endeavors to support

users to a level that is appropriate for that feature. You can contact support at https://developer.arm.com/

support.

Identification in the documentation

All features that are documented in the Arm Compiler 6 documentation are product features, except

where explicitly stated. The limitations of non-product features are explicitly stated.

Product features

Product features are suitable for use in a production environment. The functionality is well-tested, and is

expected to be stable across feature and update releases.

• Arm endeavors to give advance notice of significant functionality changes to product features.

• If you have a support and maintenance contract, Arm provides full support for use of all product

features.

• Arm welcomes feedback on product features.

• Any issues with product features that Arm encounters or is made aware of are considered for fixing in

future versions of Arm Compiler.

In addition to fully supported product features, some product features are only alpha or beta quality.

Beta product features

Beta product features are implementation complete, but have not been sufficiently tested to be

regarded as suitable for use in production environments.

Beta product features are indicated with [BETA].

• Arm endeavors to document known limitations on beta product features.

• Beta product features are expected to eventually become product features in a future release

of Arm Compiler 6.

• Arm encourages the use of beta product features, and welcomes feedback on them.

• Any issues with beta product features that Arm encounters or is made aware of are

considered for fixing in future versions of Arm Compiler.

Alpha product features

Alpha product features are not implementation complete, and are subject to change in future

releases, therefore the stability level is lower than in beta product features.

Alpha product features are indicated with [ALPHA].

• Arm endeavors to document known limitations of alpha product features.

• Arm encourages the use of alpha product features, and welcomes feedback on them.

• Any issues with alpha product features that Arm encounters or is made aware of are

considered for fixing in future versions of Arm Compiler.

Community features

Arm Compiler 6 is built on LLVM technology and preserves the functionality of that technology where

possible. This means that there are additional features available in Arm Compiler that are not listed in the

documentation. These additional features are known as Community features. For information on these

Community features, see the documentation for the Clang/LLVM project.

1 Compiler Command-line Options

1.1 Support level definitions

DUI0774K Copyright © 2014–2017, 2019, 2020 Arm Limited or its affiliates. All

rights reserved.

1-19

Non-Confidential

Where Community features are referenced in the documentation, they are indicated with

[COMMUNITY].

• Arm makes no claims about the quality level or the degree of functionality of these features, except

when explicitly stated in this documentation.

• Functionality might change significantly between feature releases.

• Arm makes no guarantees that Community features will remain functional across update releases,

although changes are expected to be unlikely.

Some Community features might become product features in the future, but Arm provides no roadmap

for this. Arm is interested in understanding your use of these features, and welcomes feedback on them.

Arm supports customers using these features on a best-effort basis, unless the features are unsupported.

Arm accepts defect reports on these features, but does not guarantee that these issues will be fixed in

future releases.

Guidance on use of Community features

There are several factors to consider when assessing the likelihood of a Community feature being

functional:

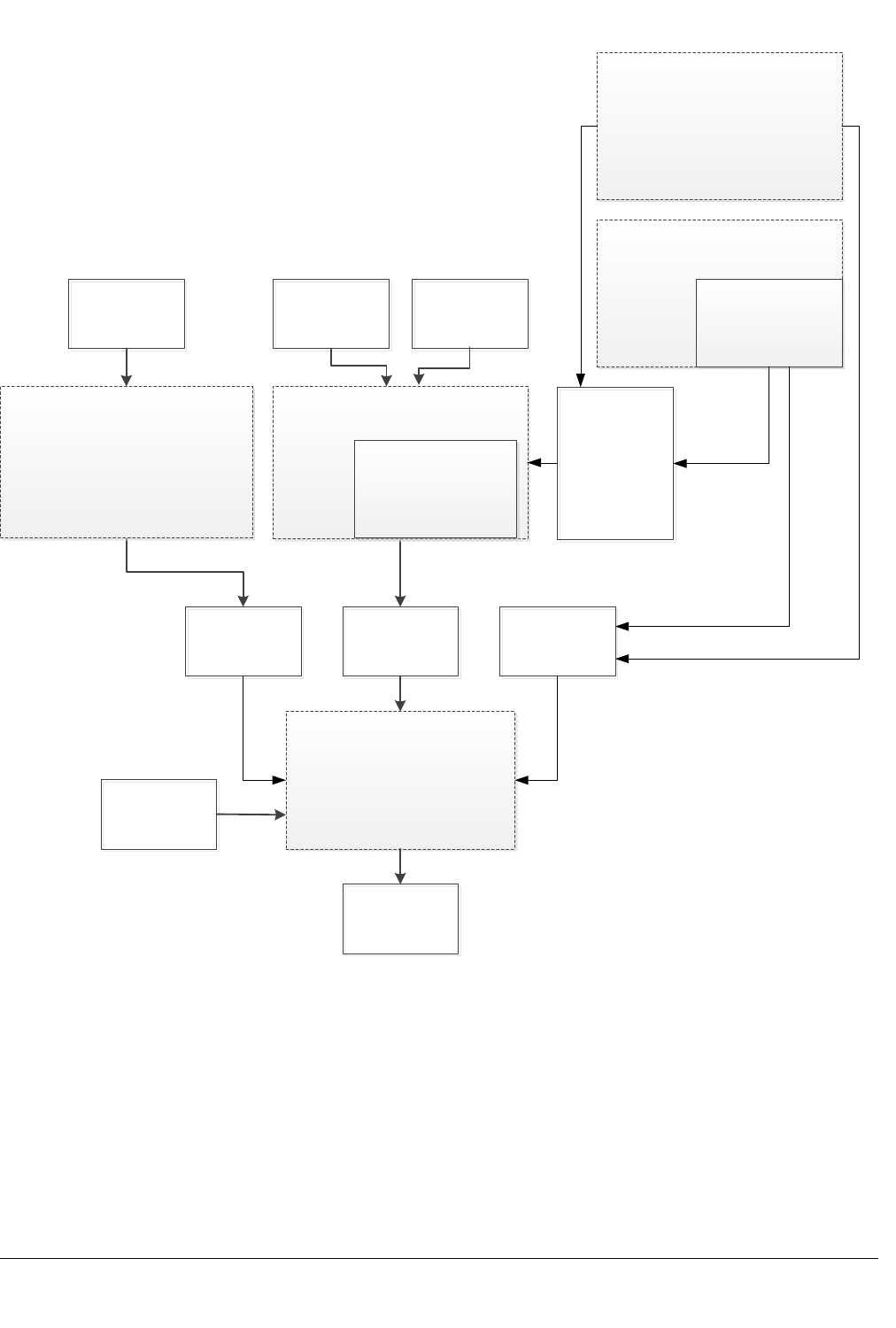

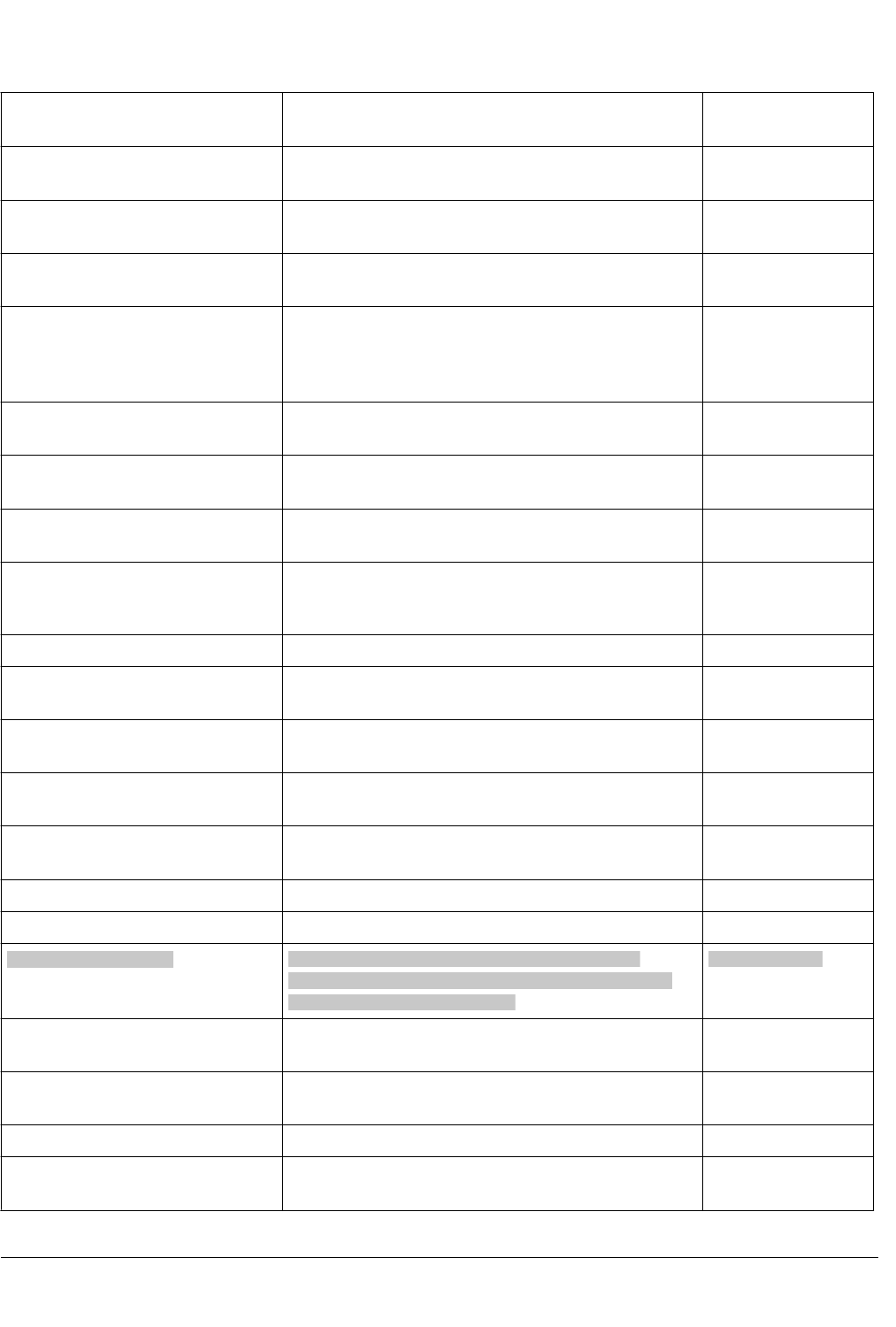

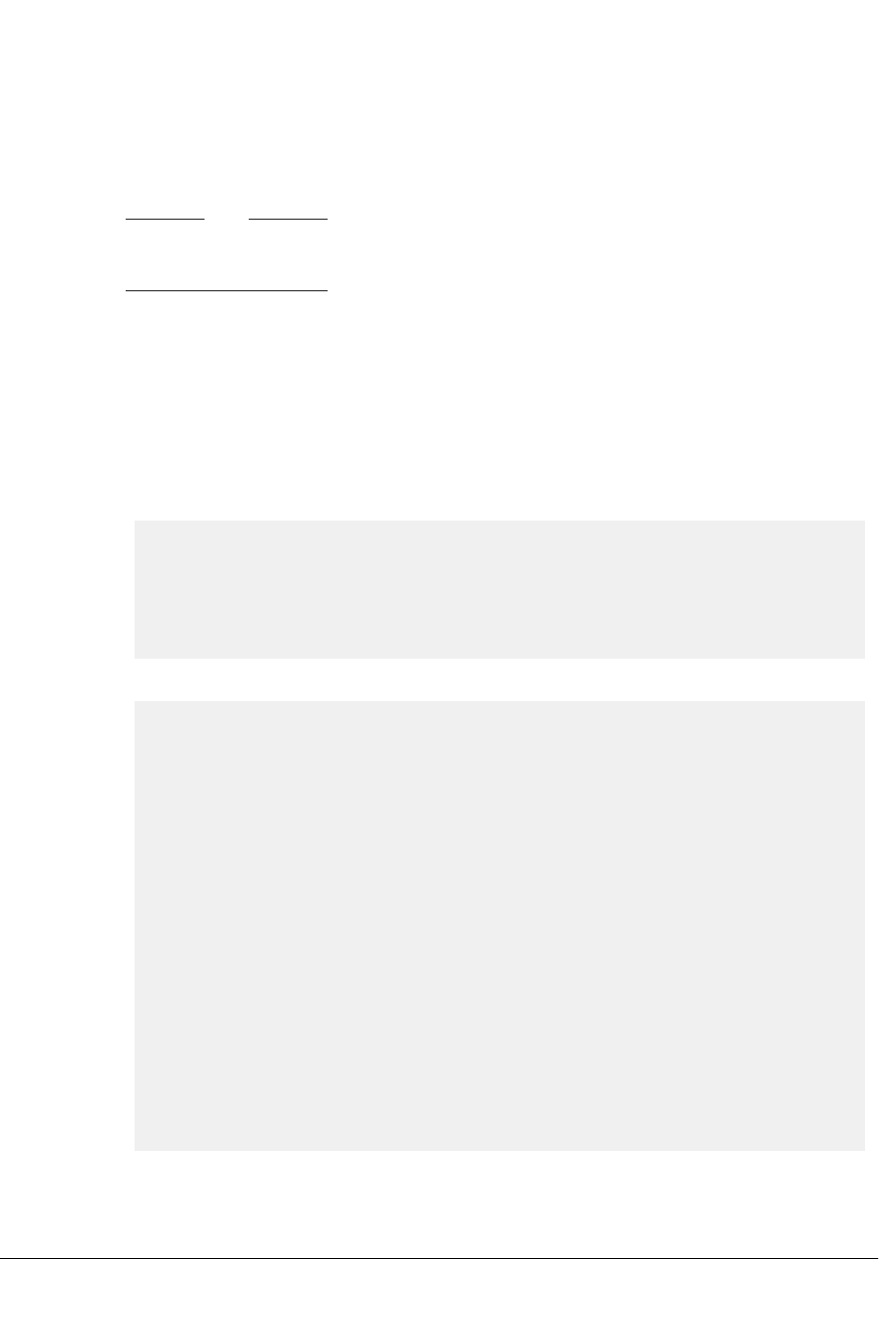

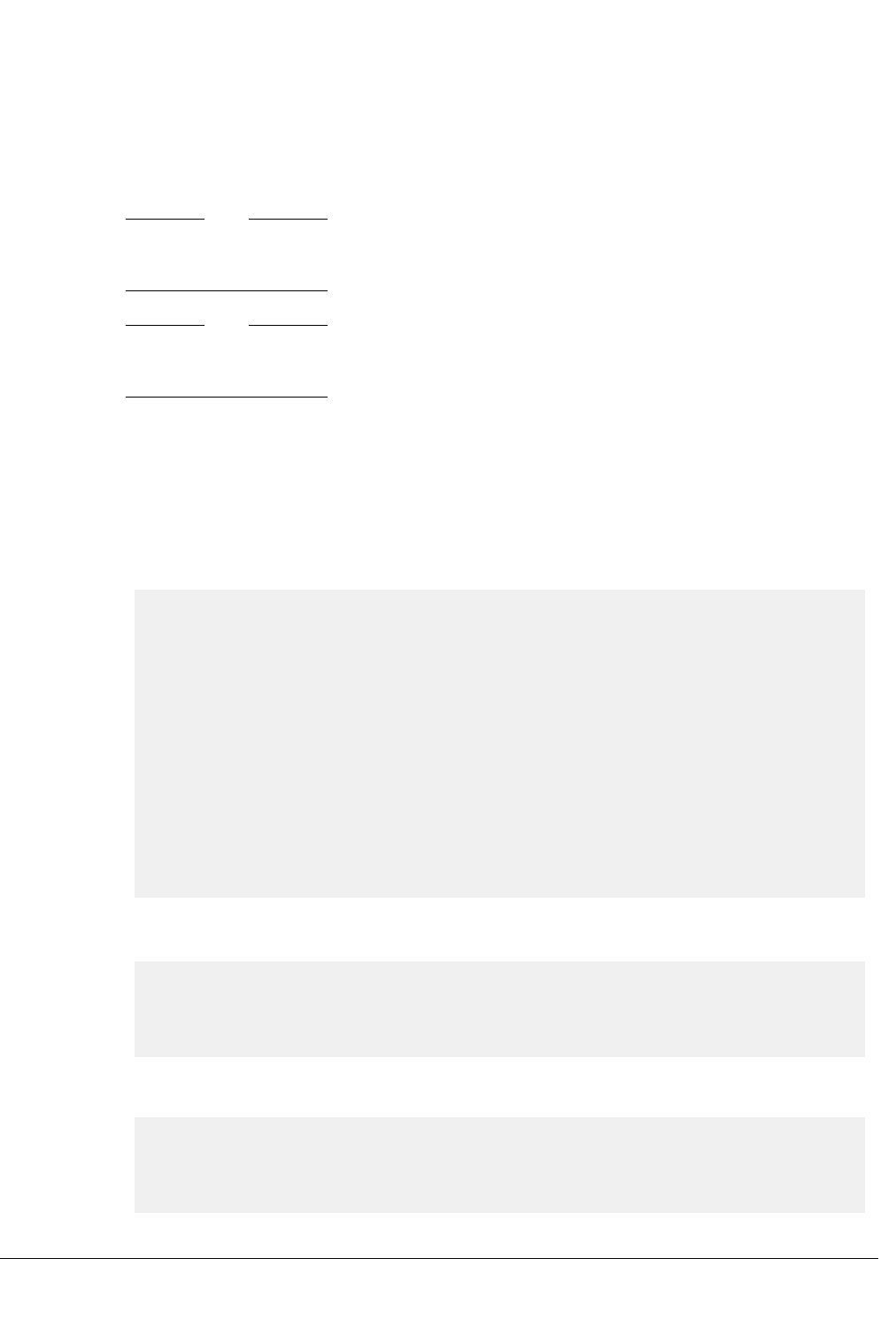

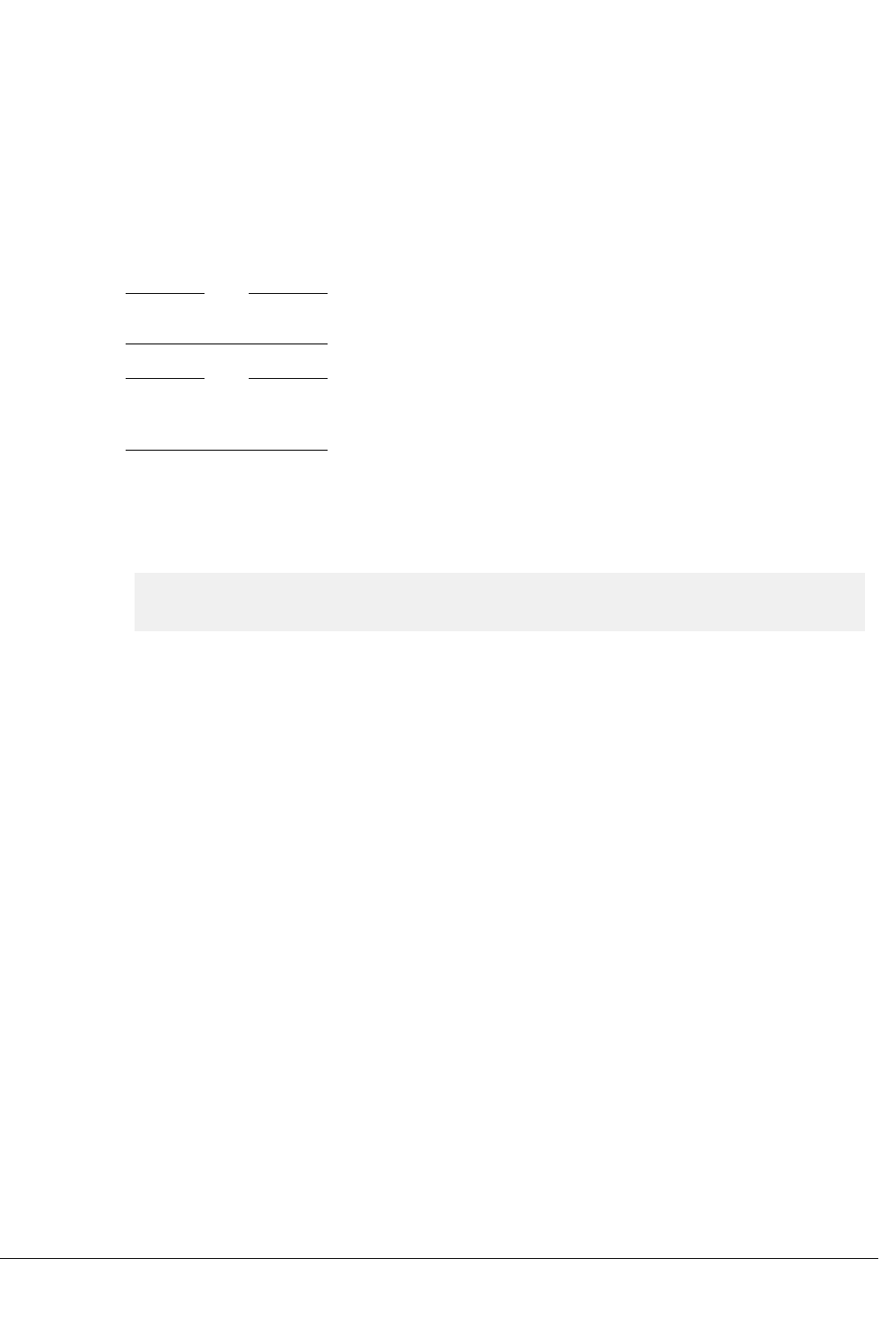

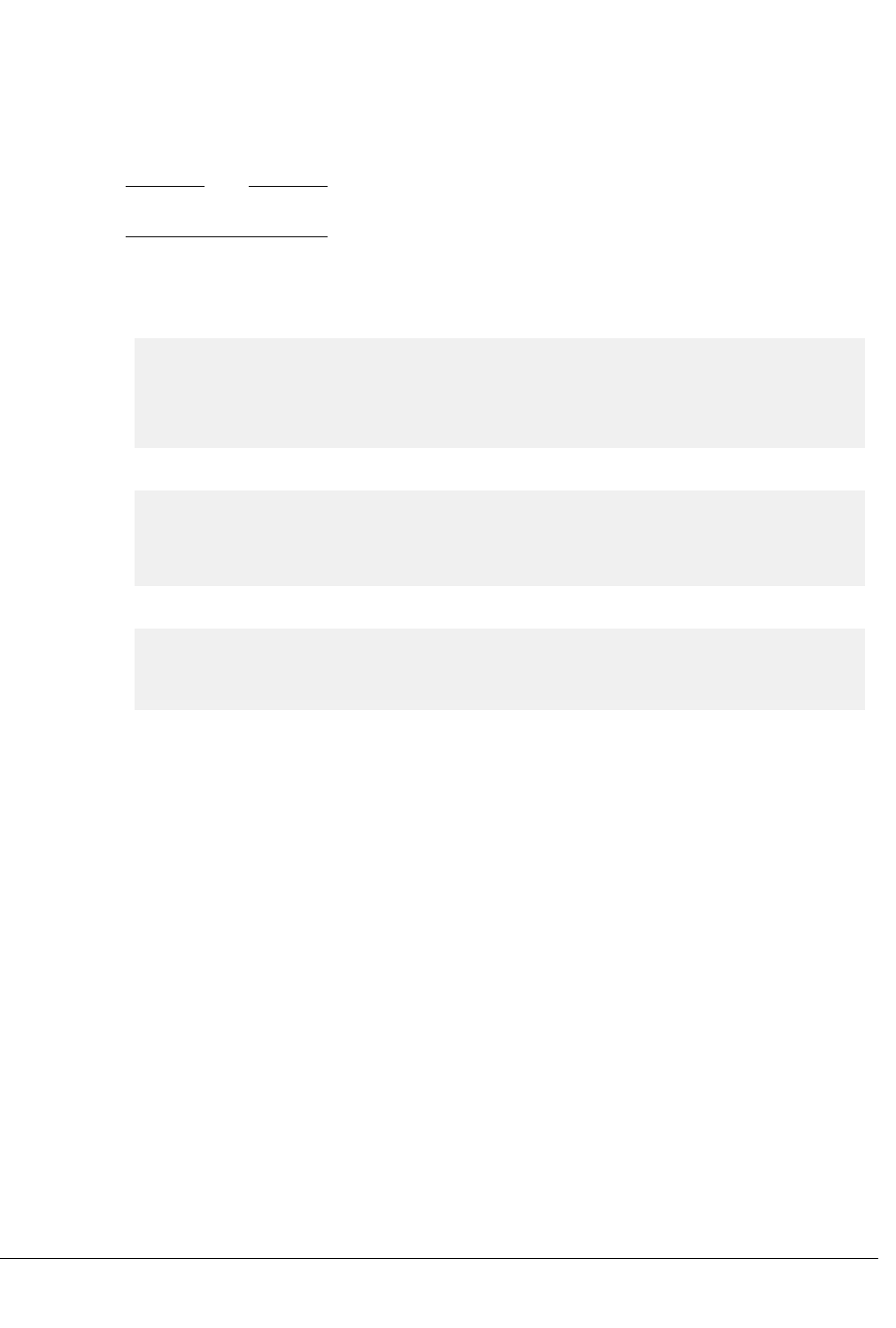

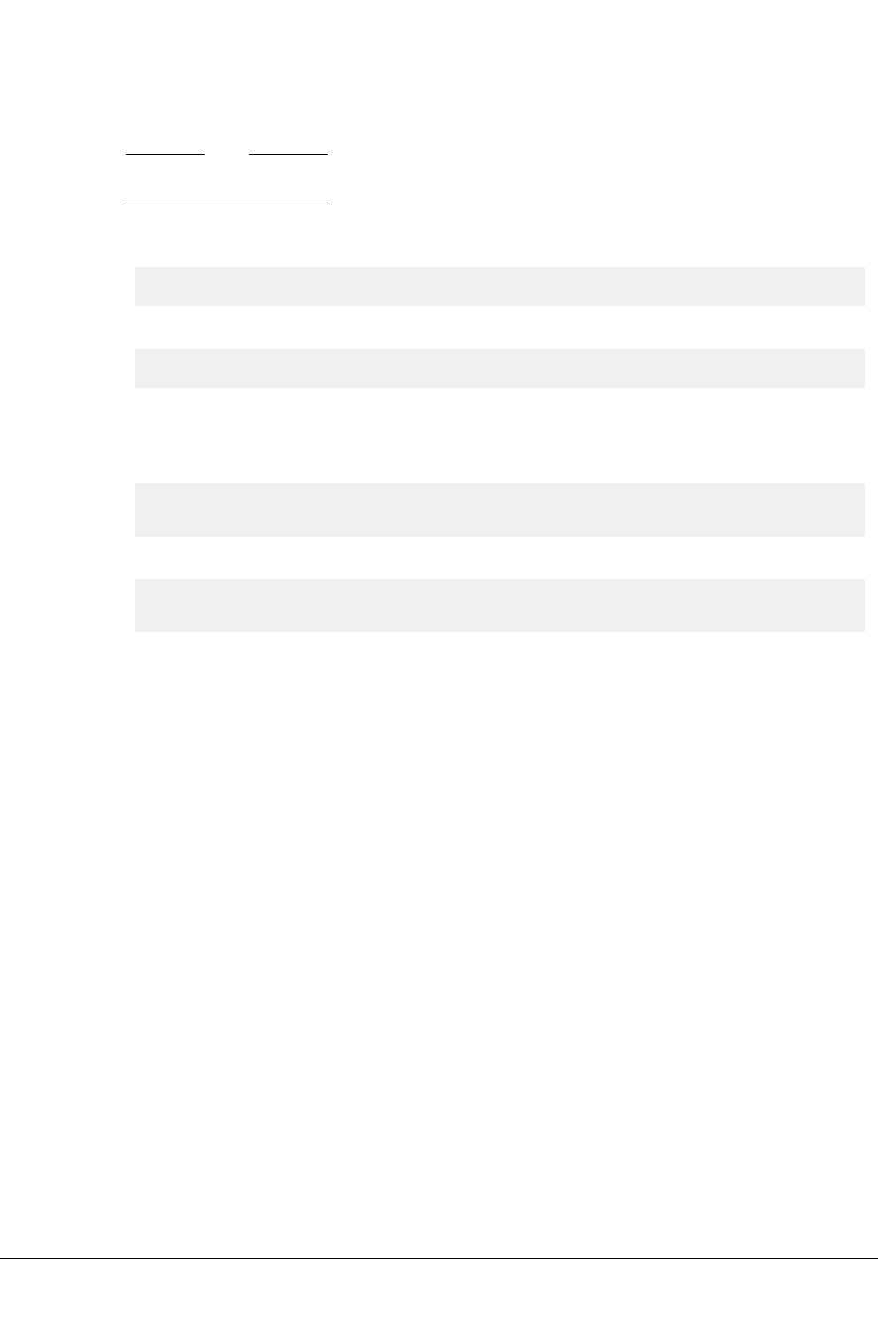

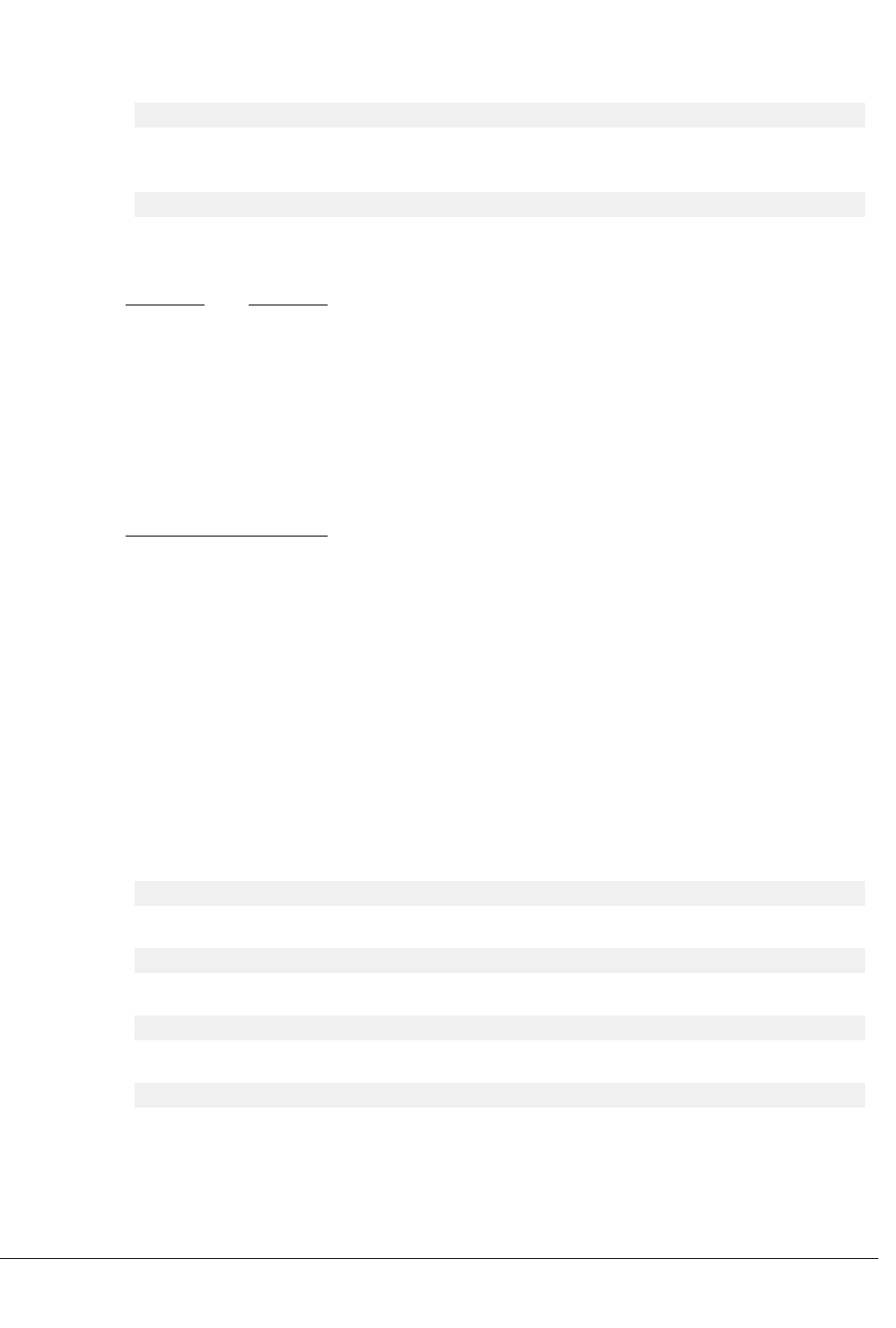

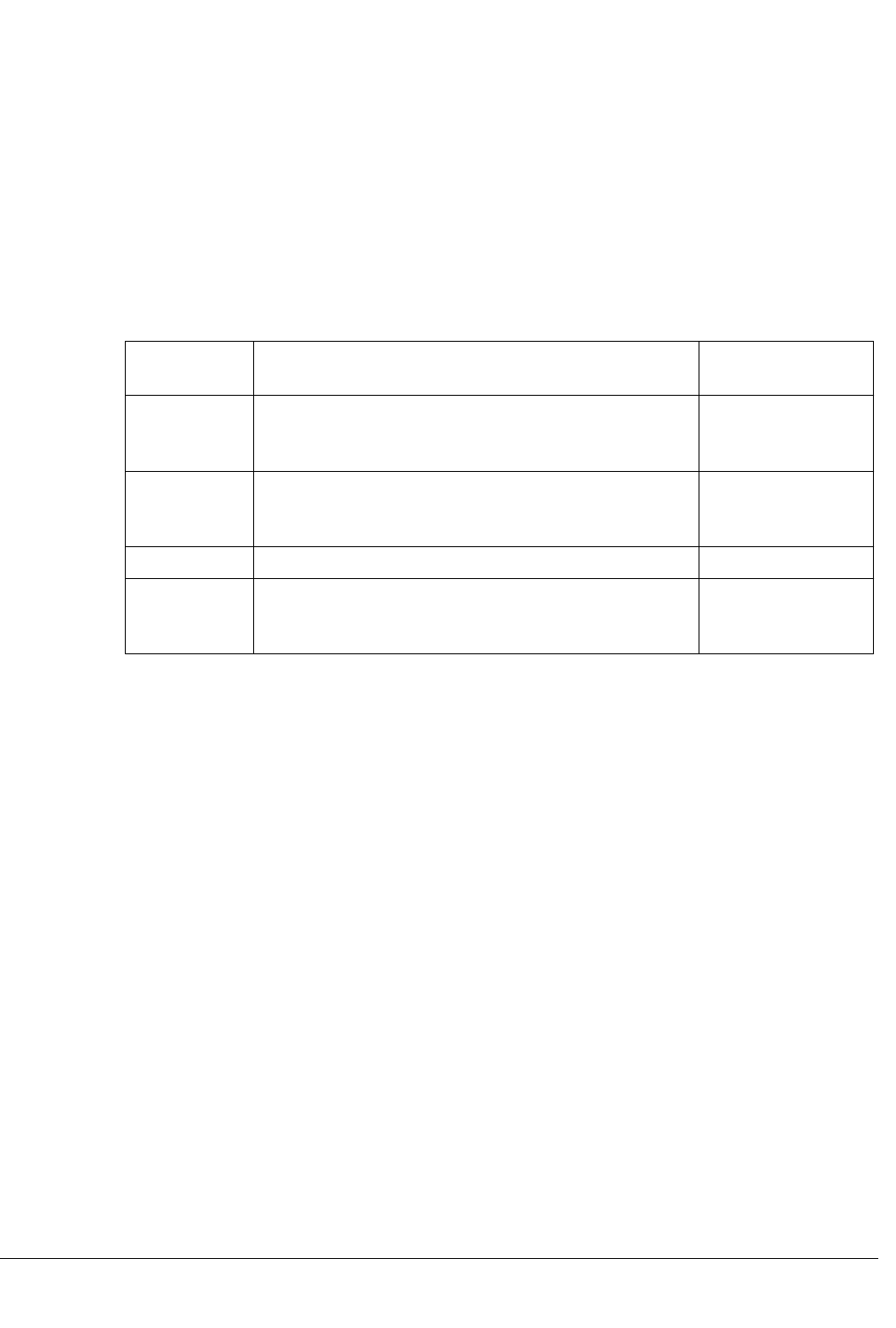

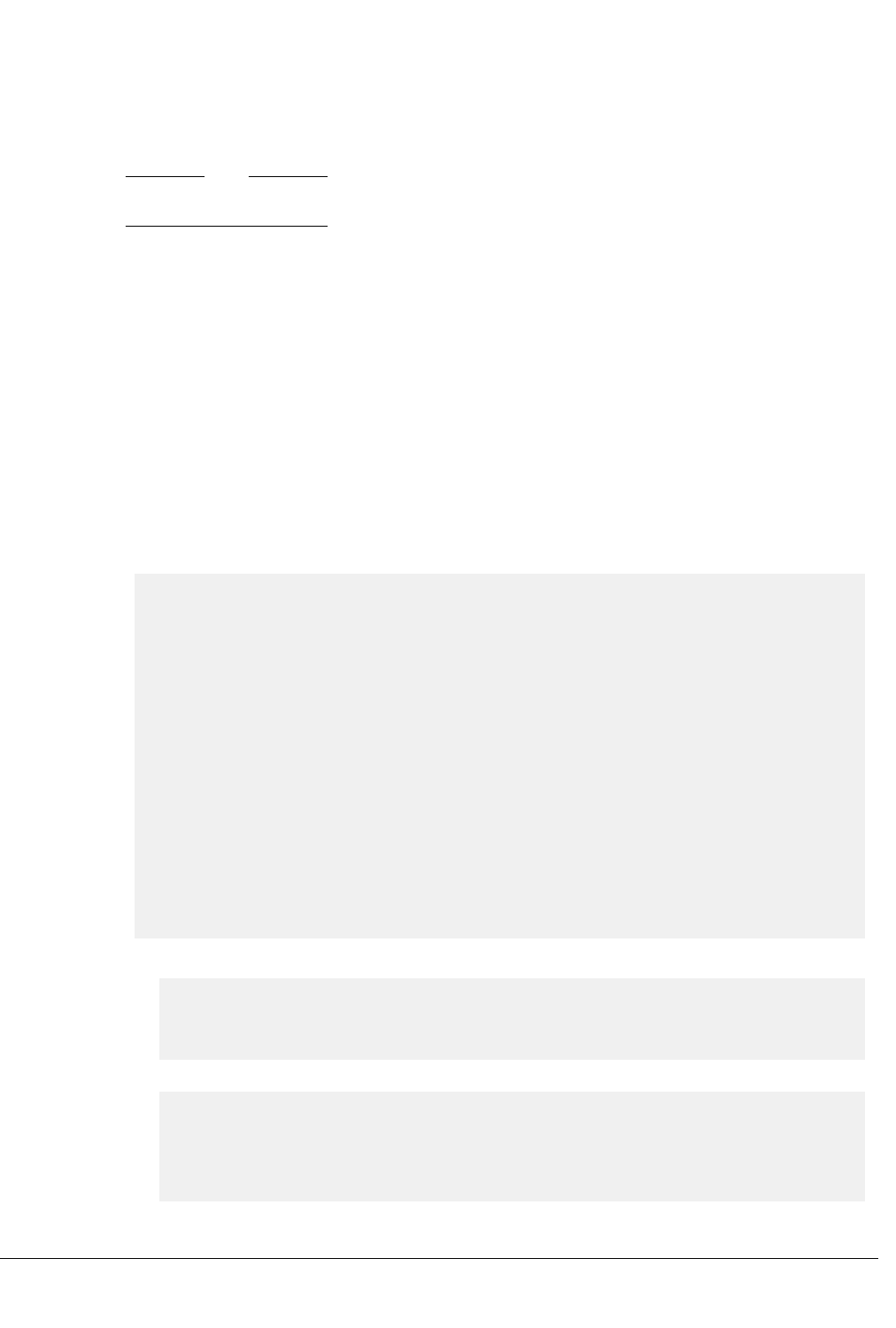

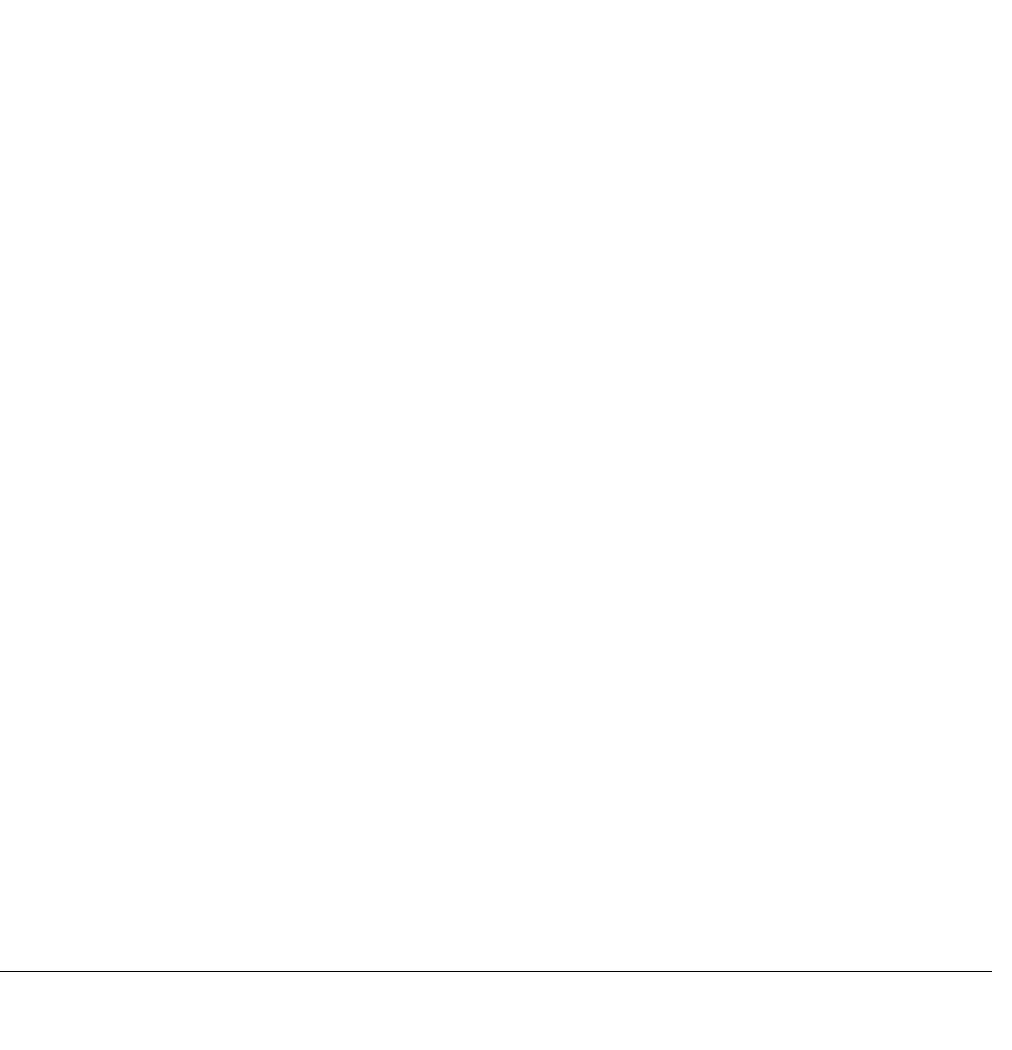

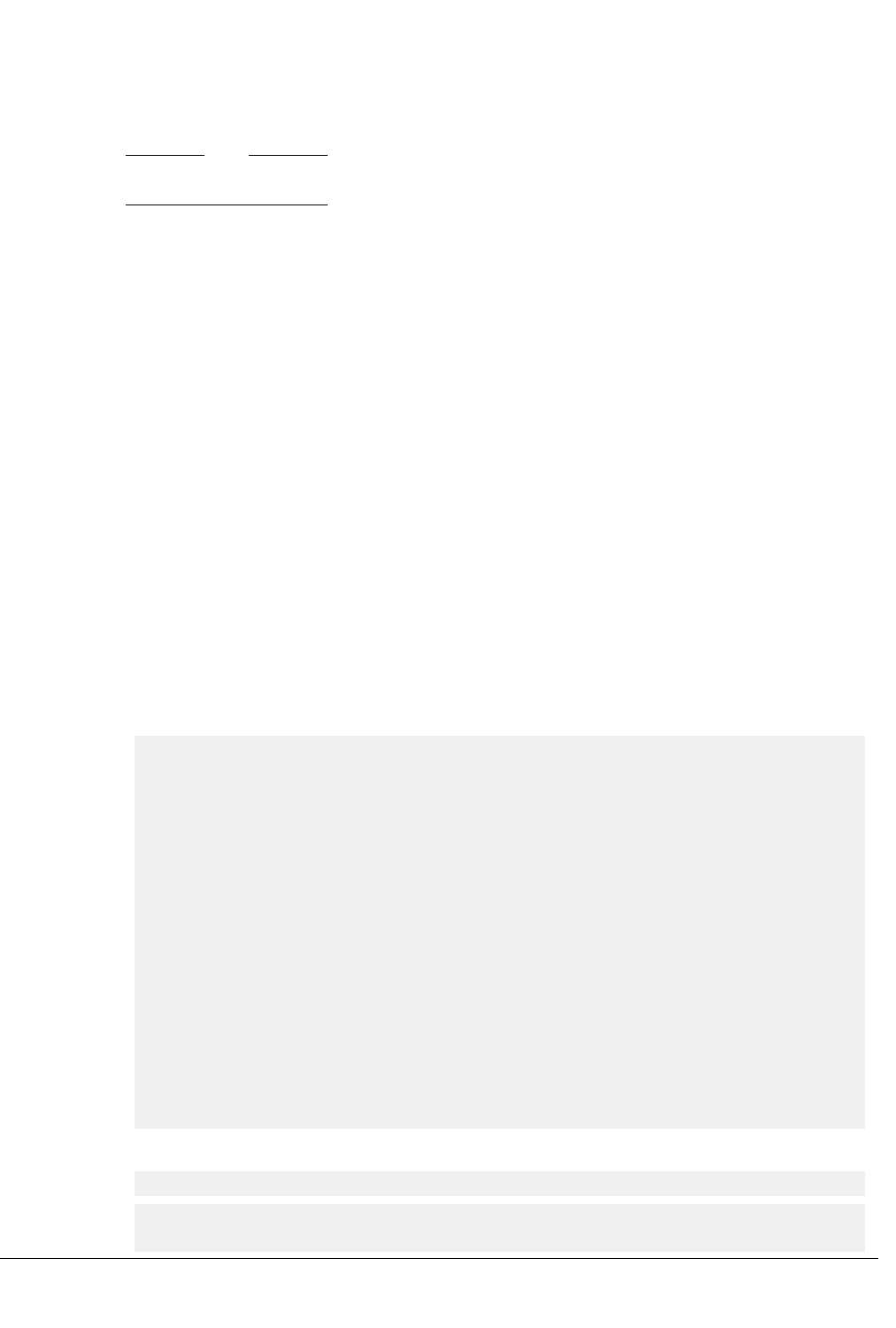

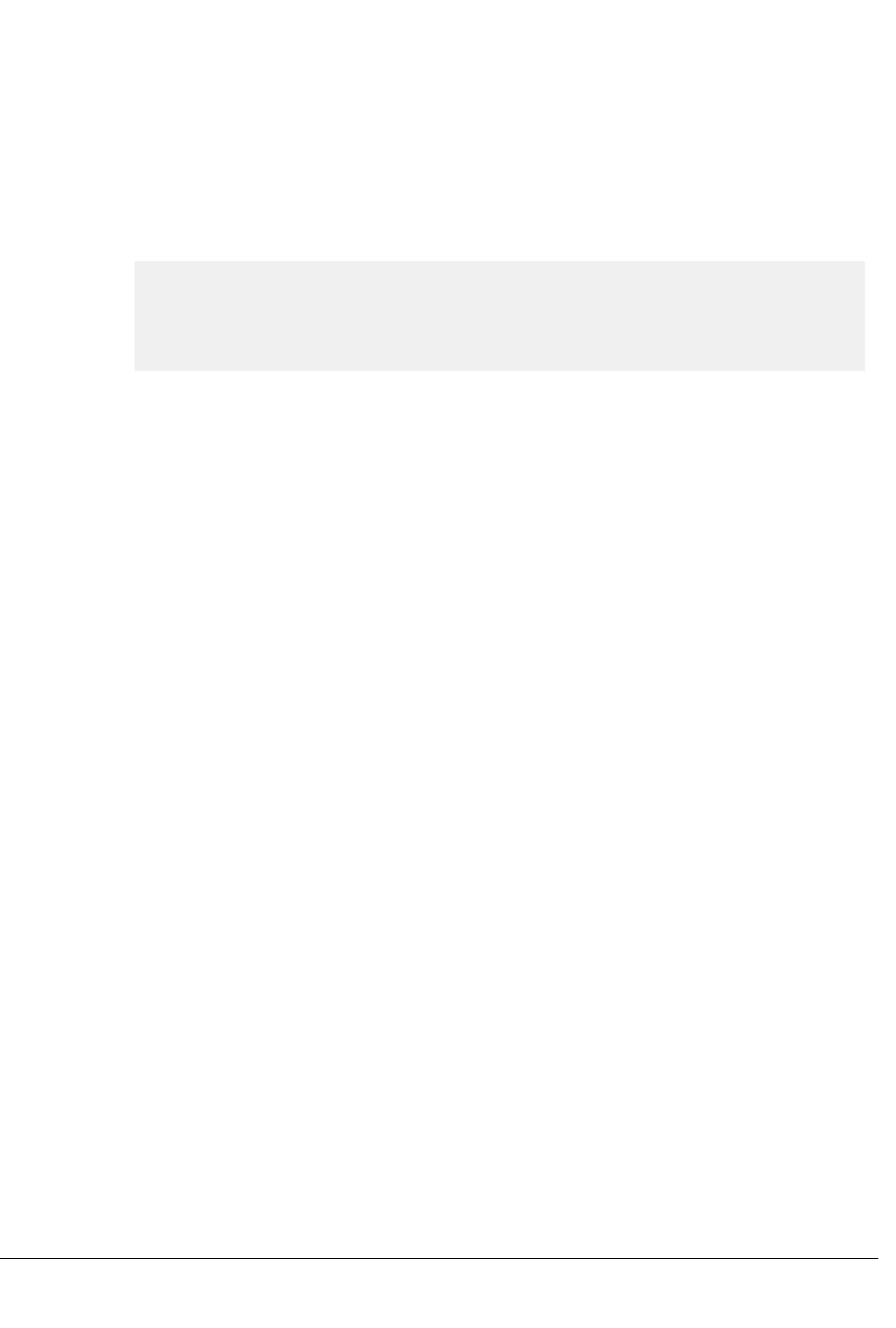

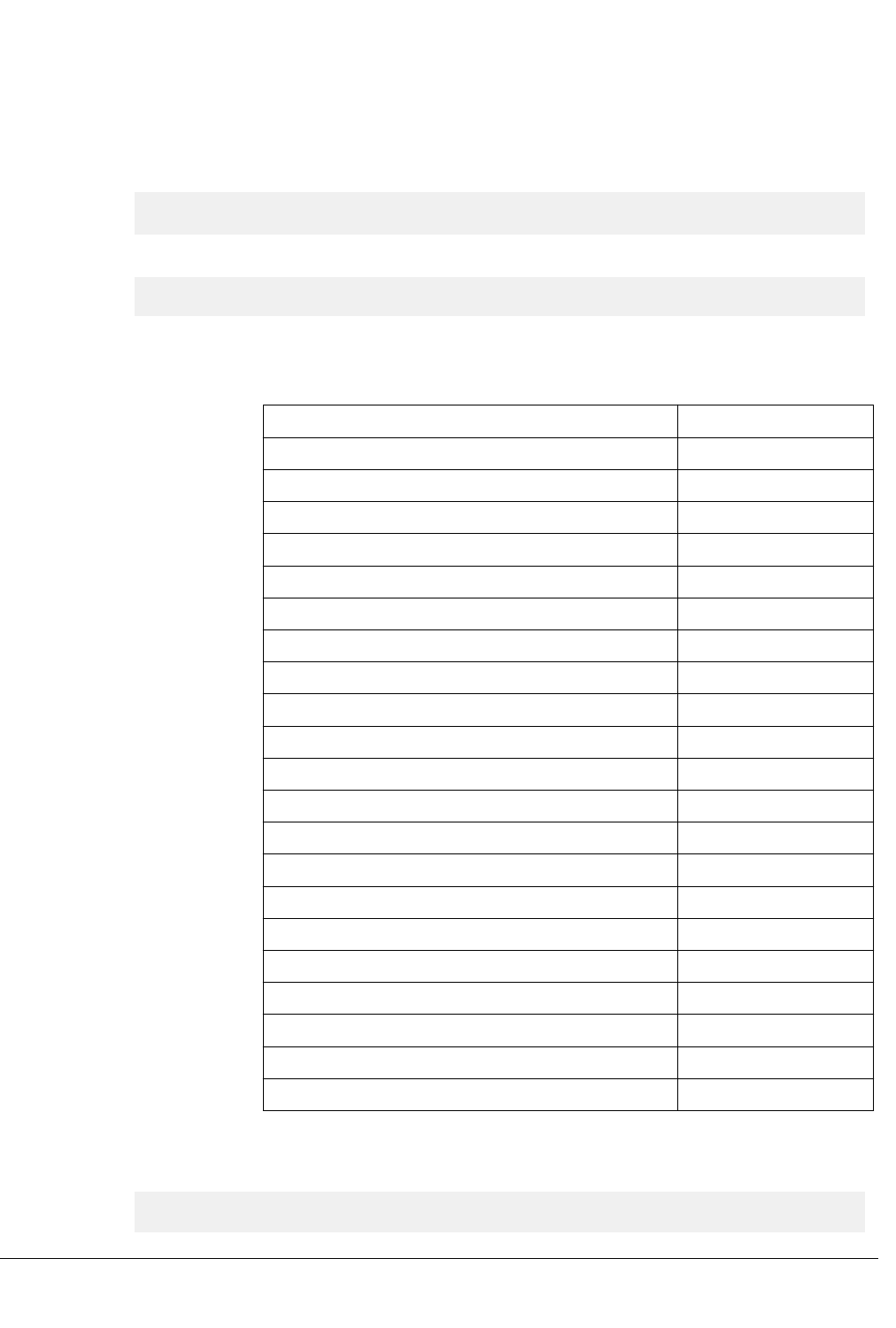

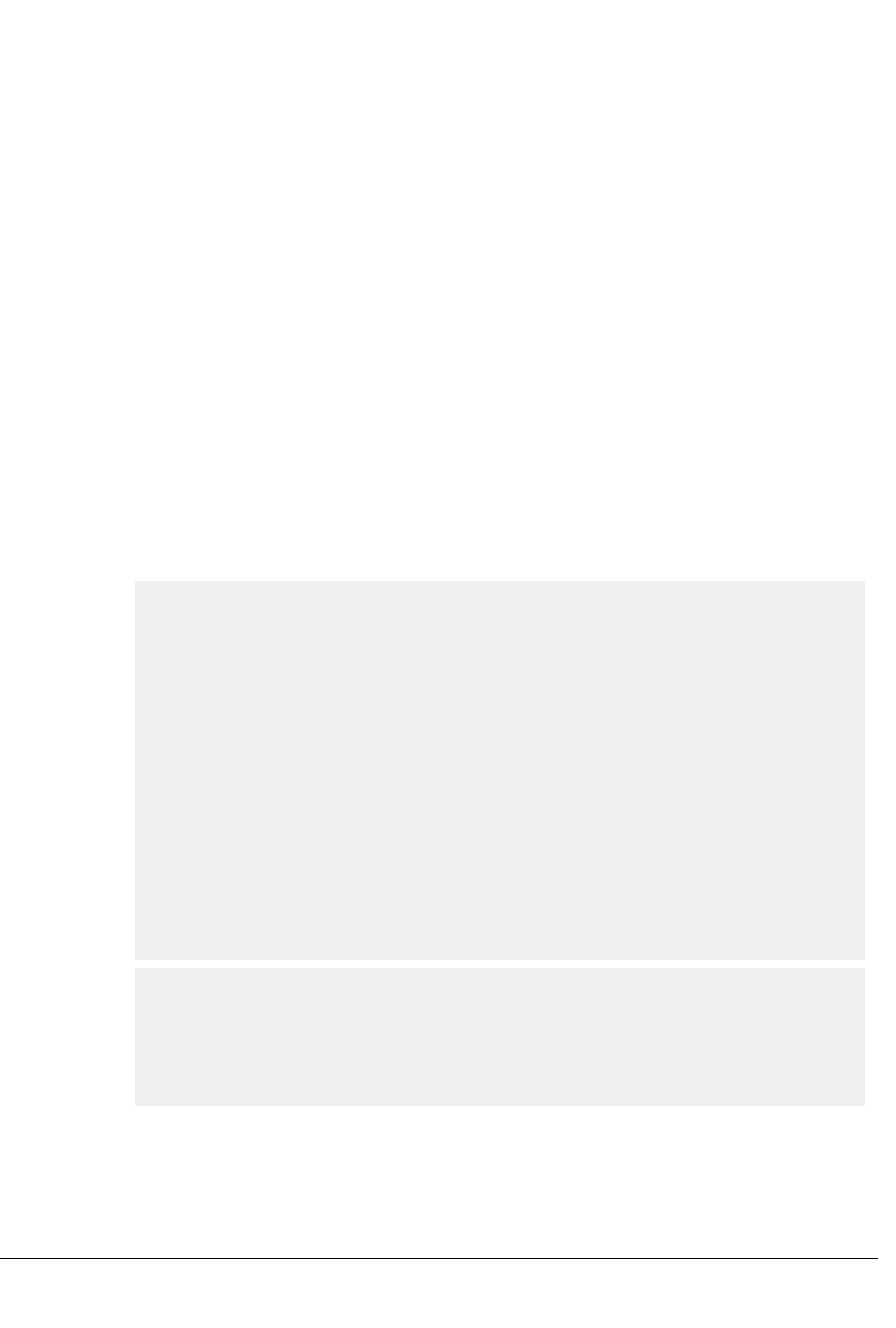

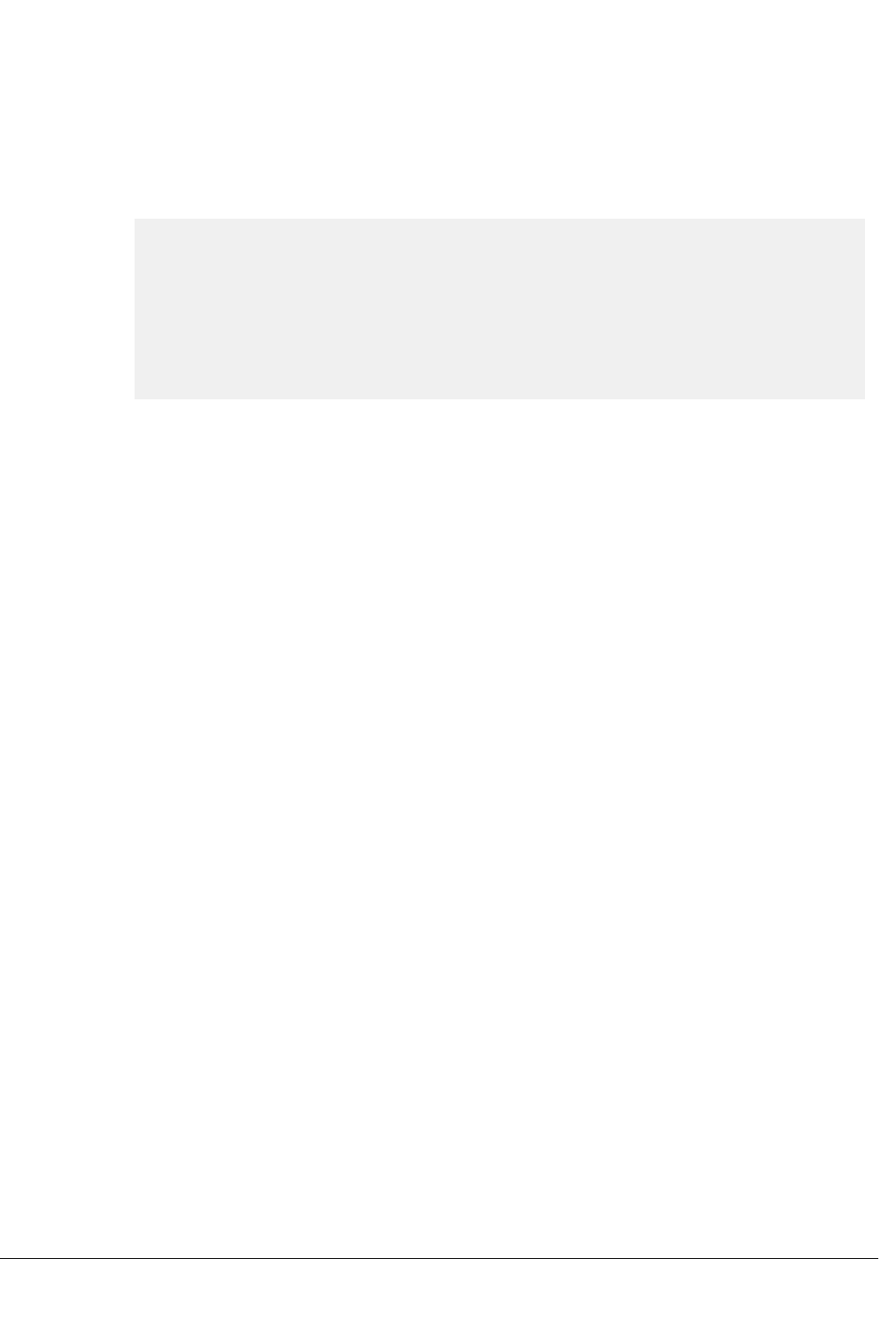

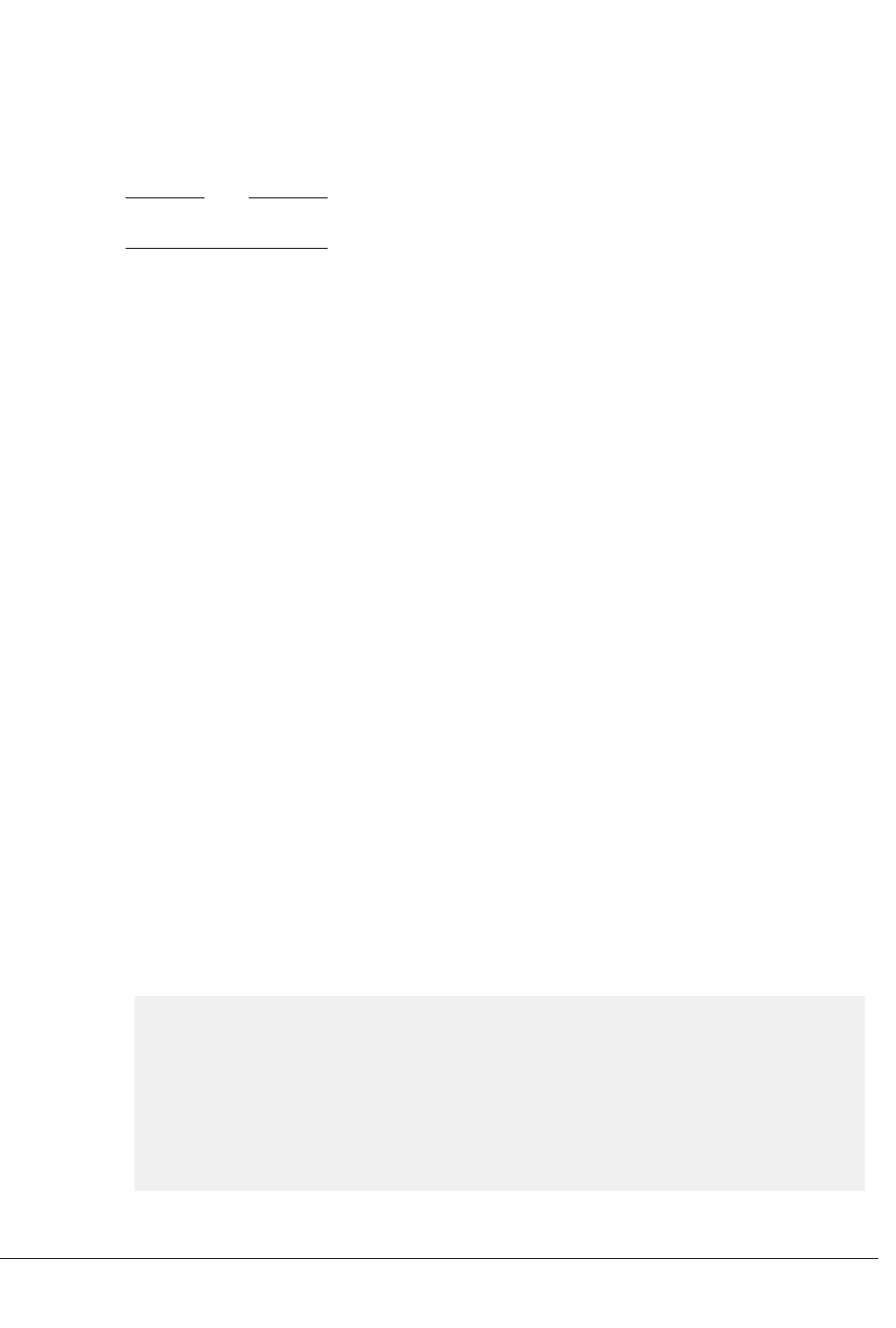

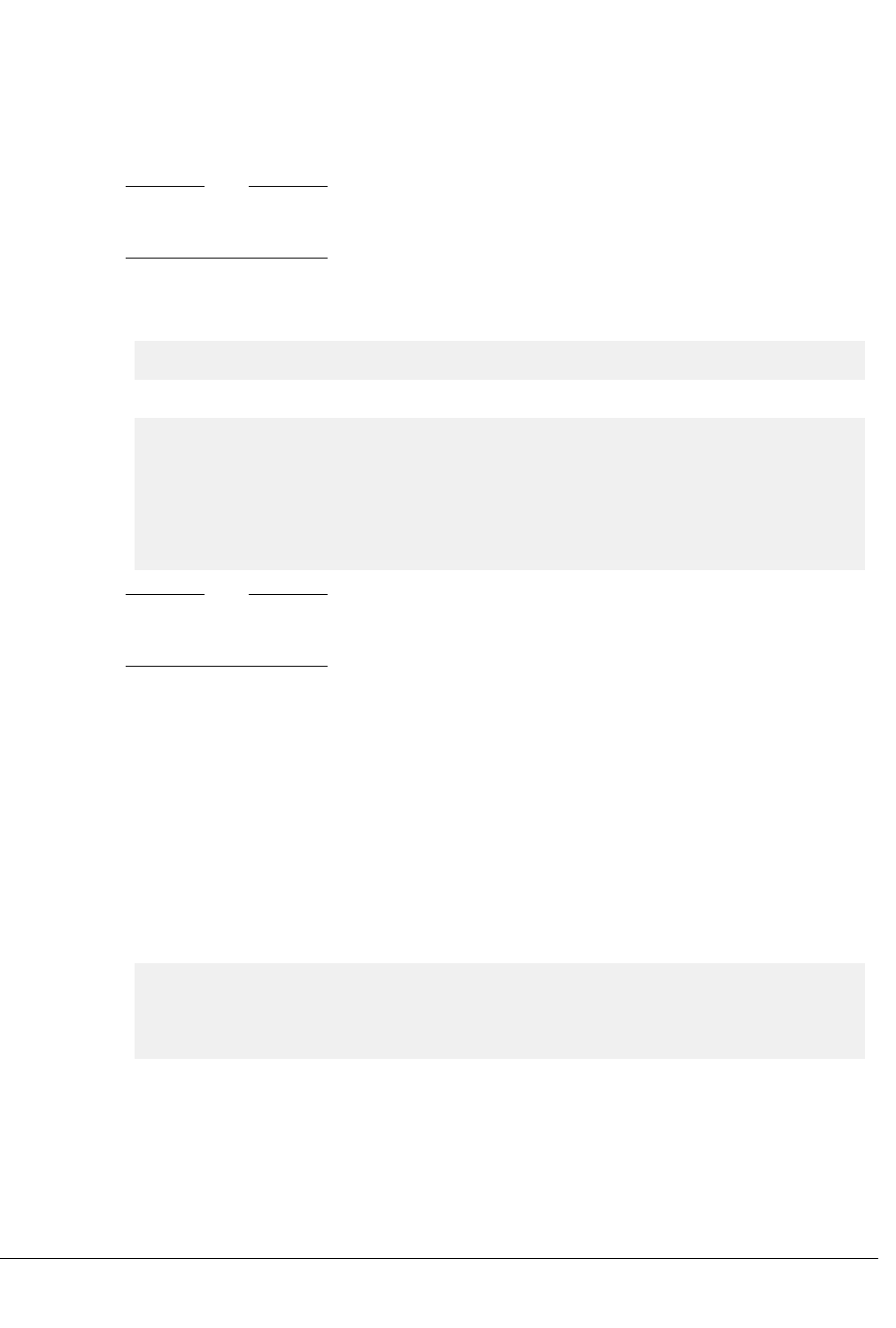

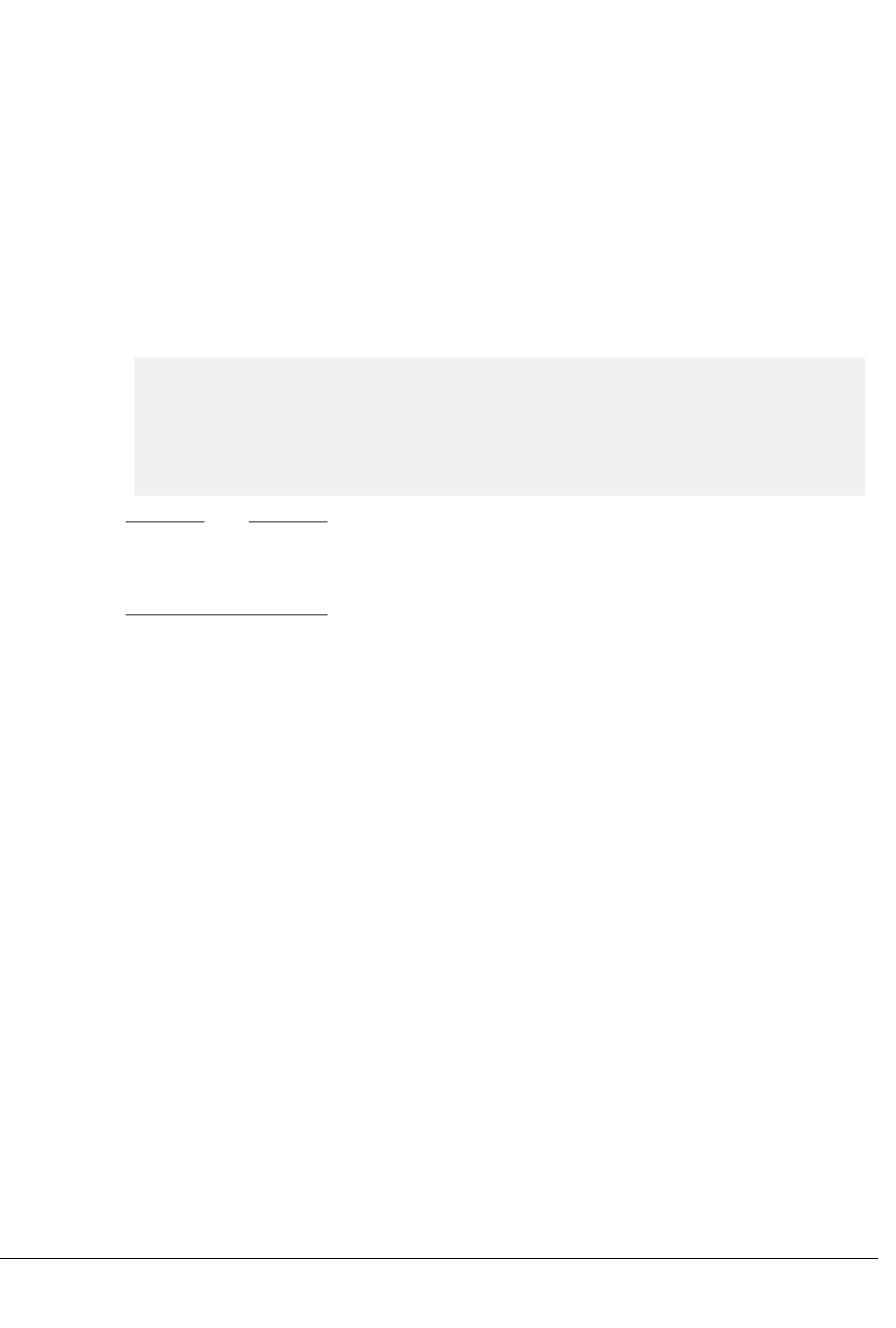

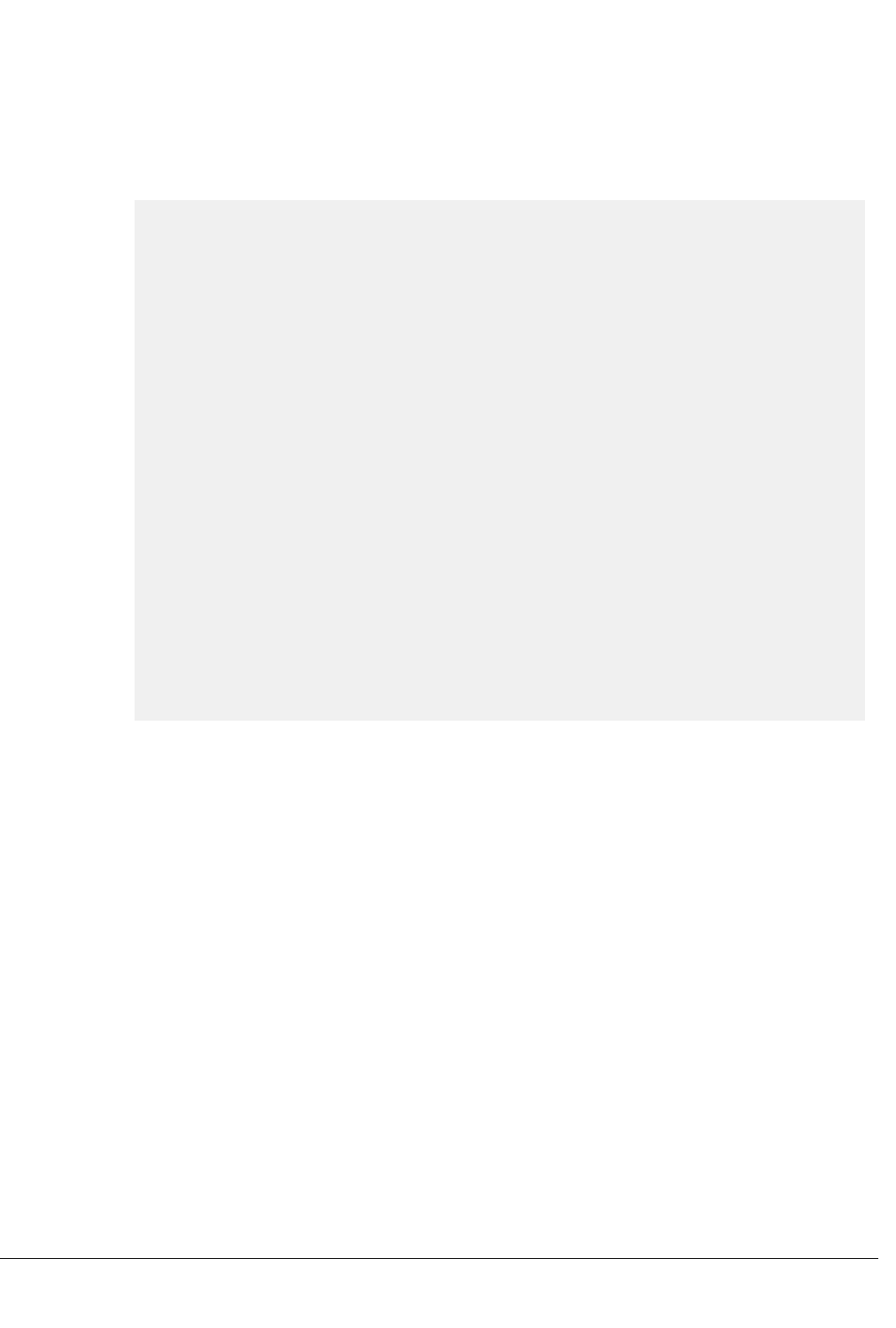

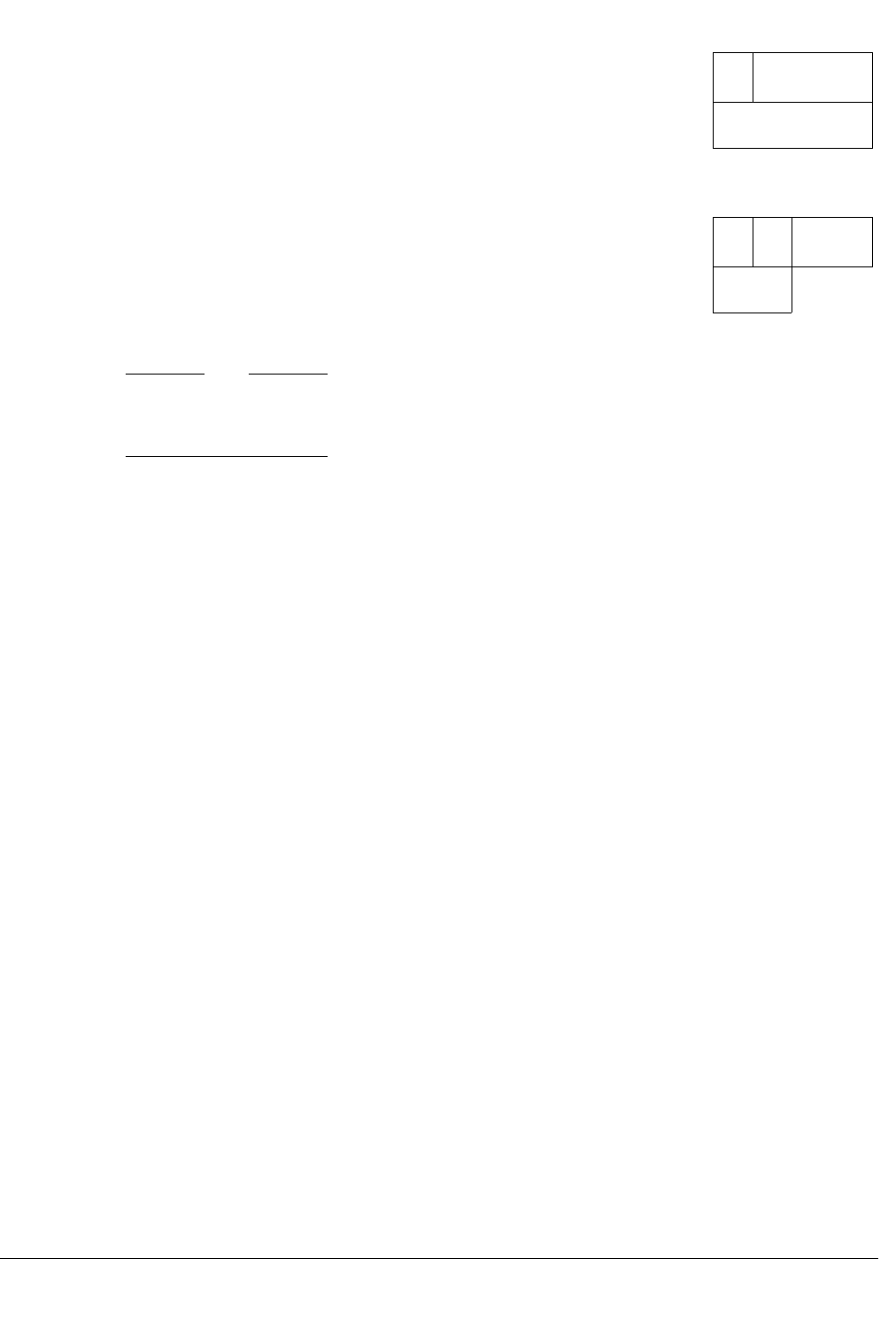

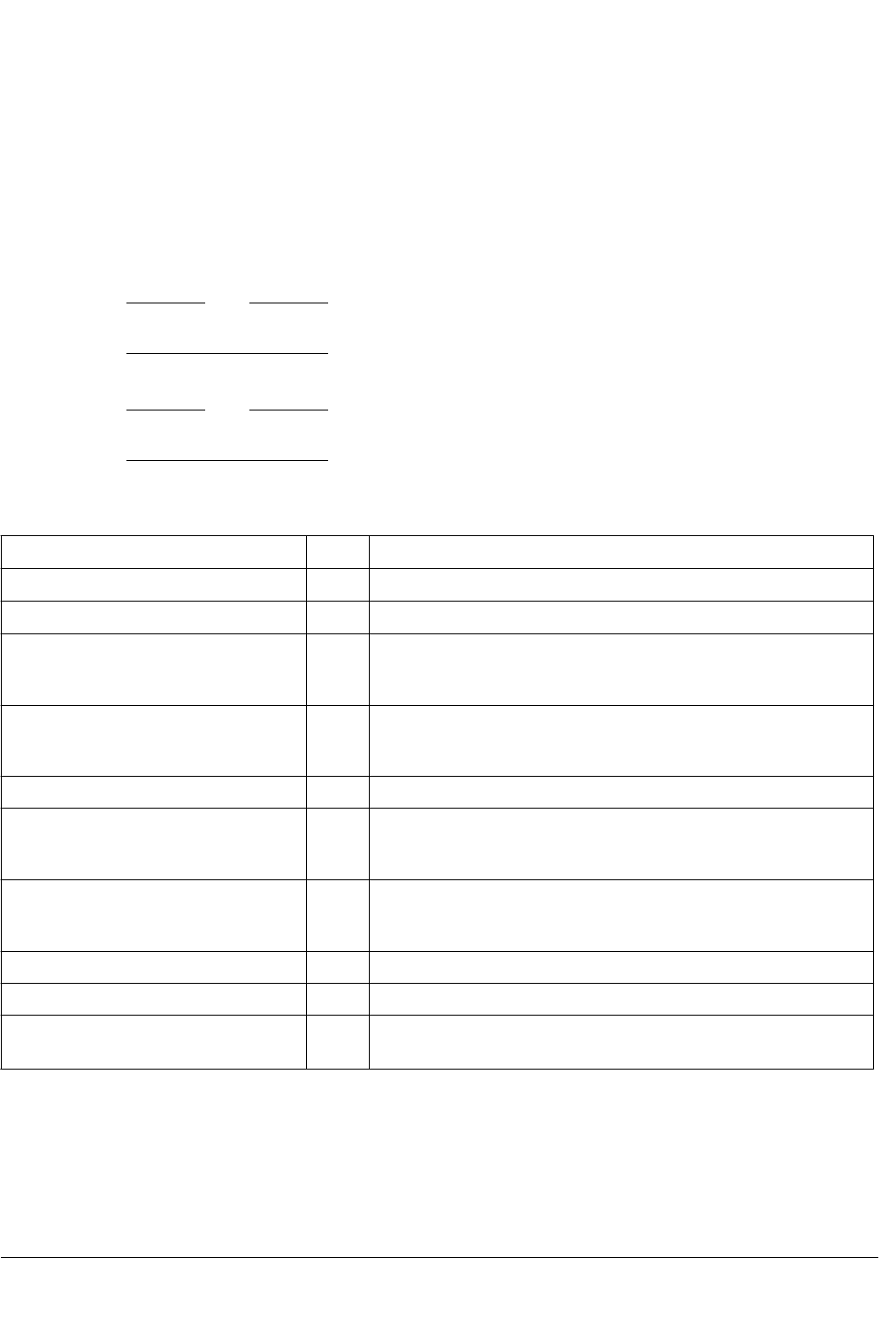

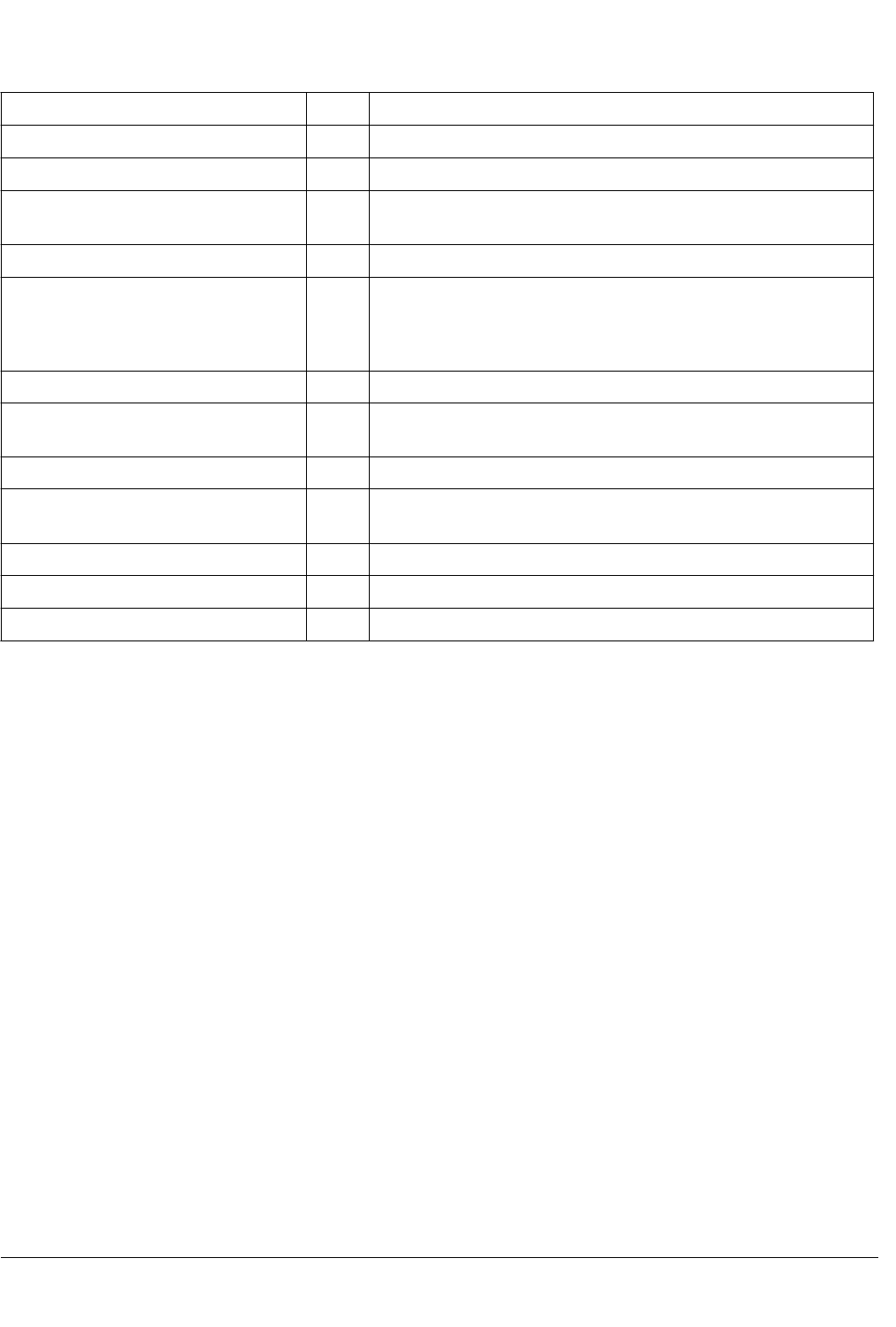

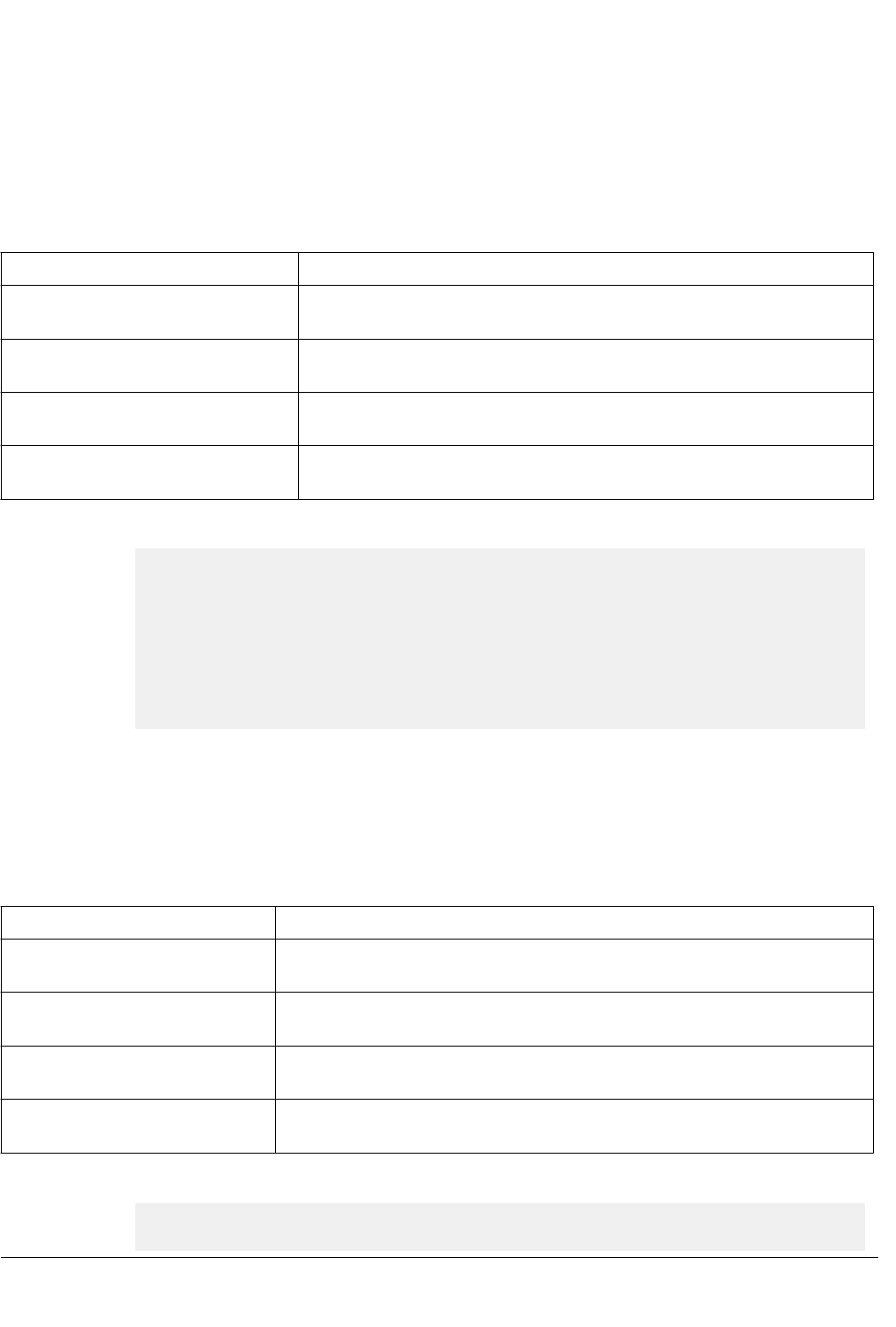

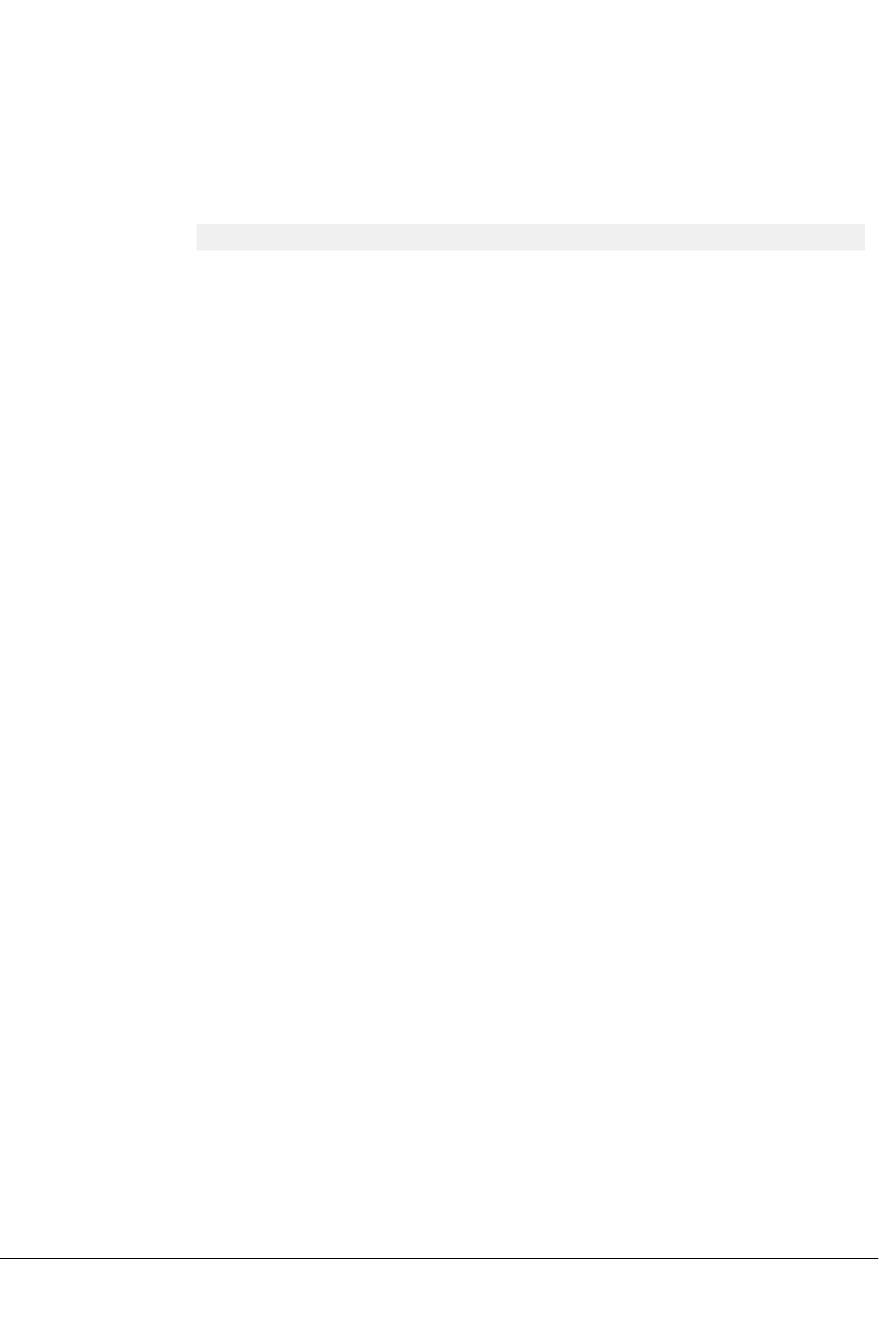

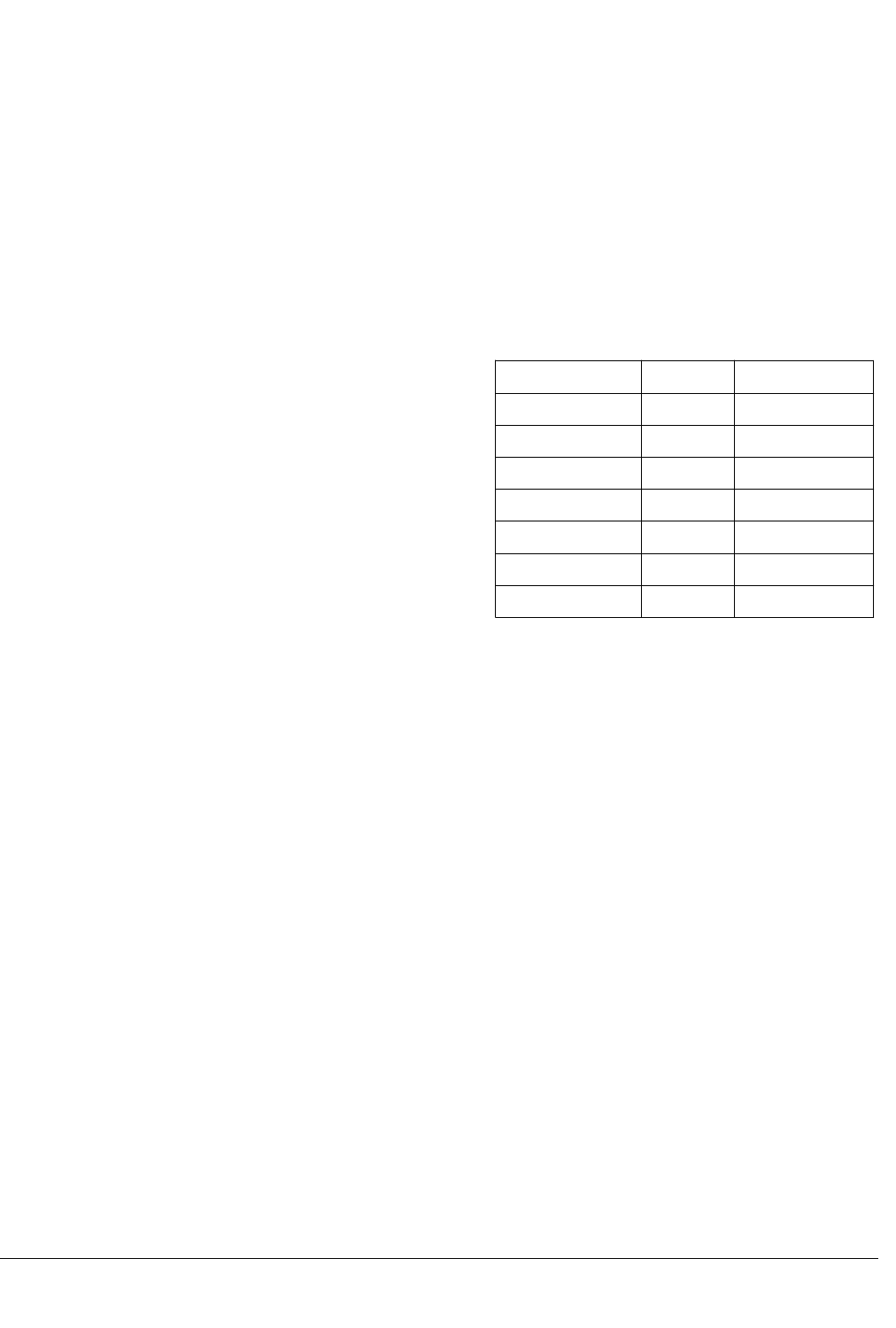

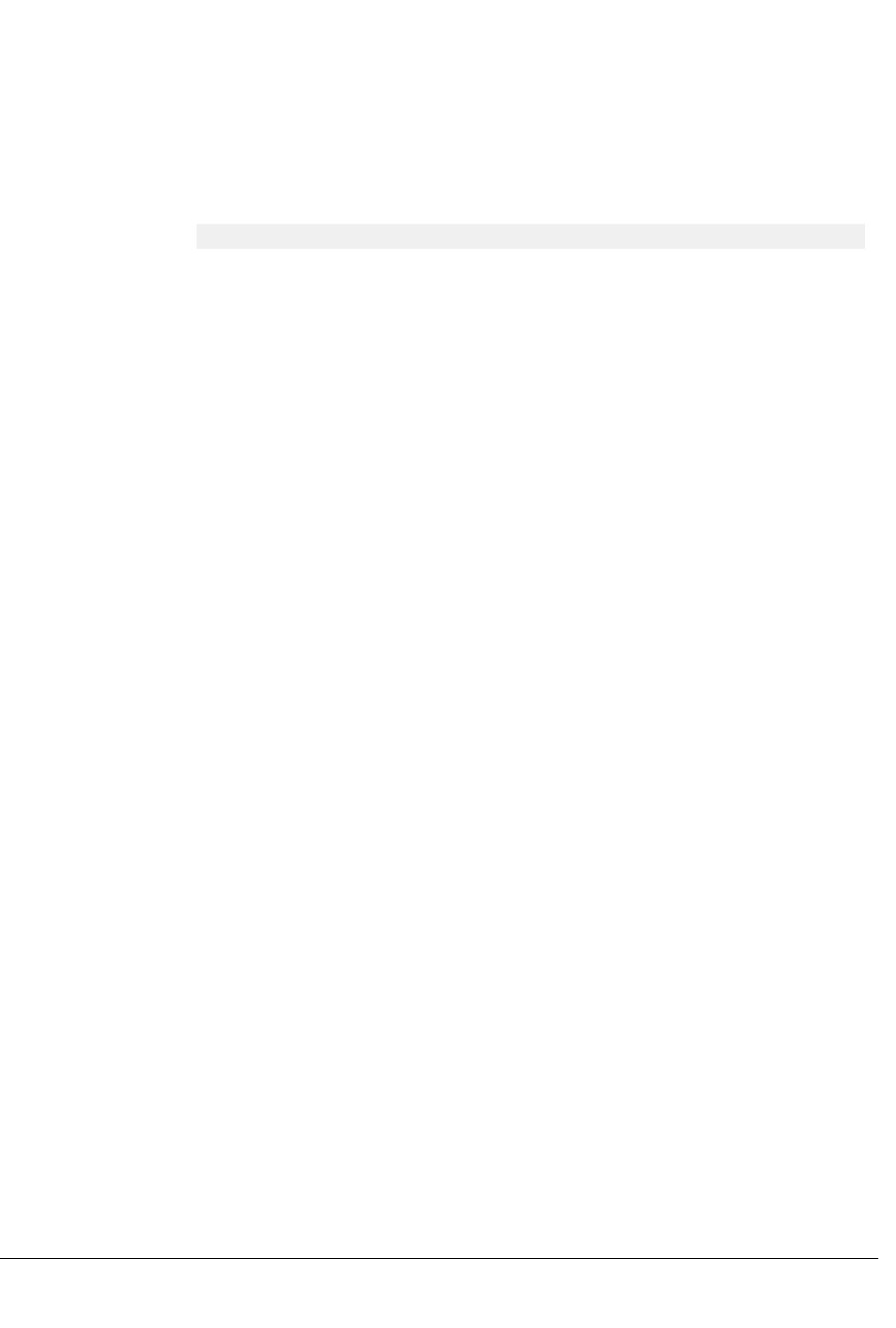

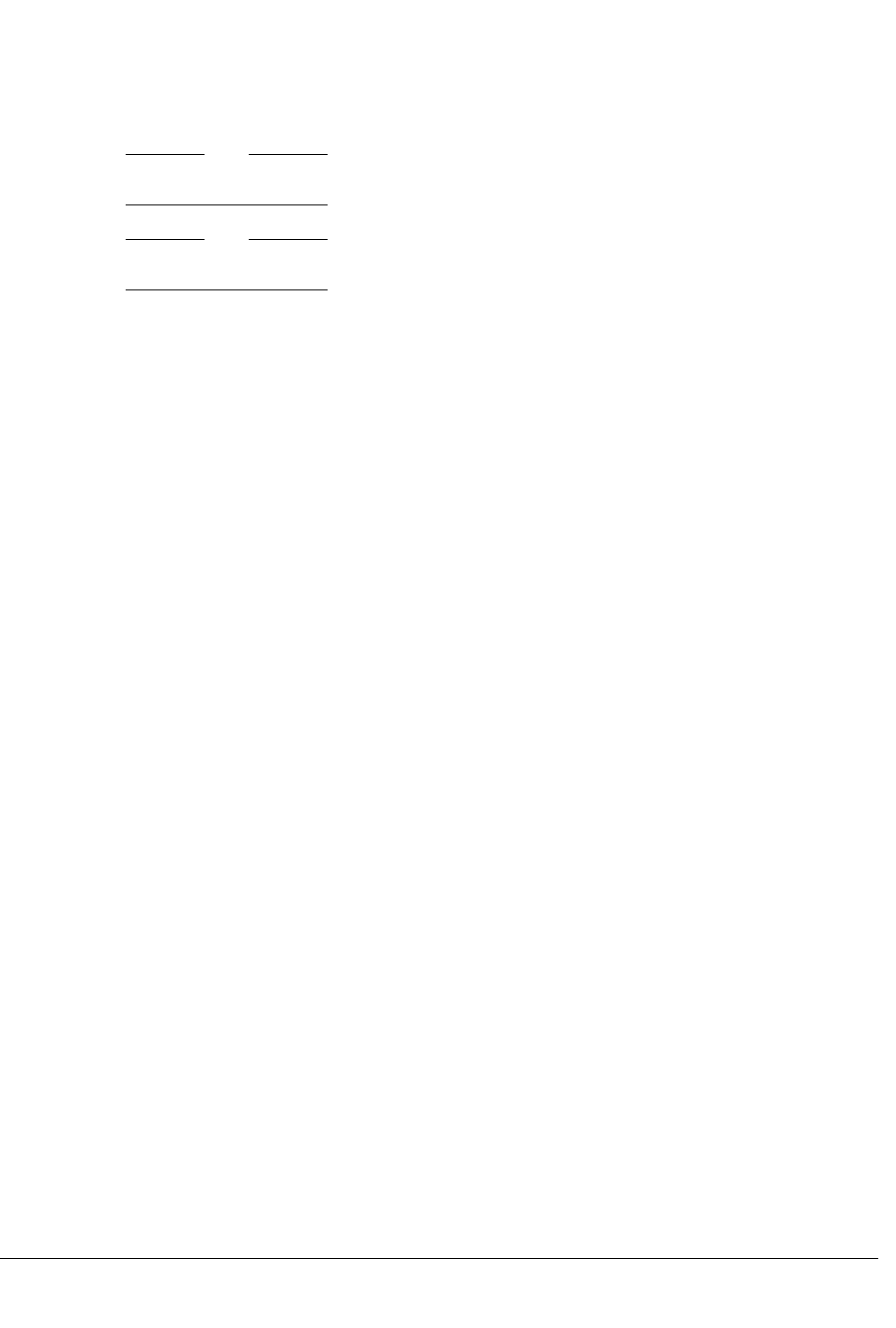

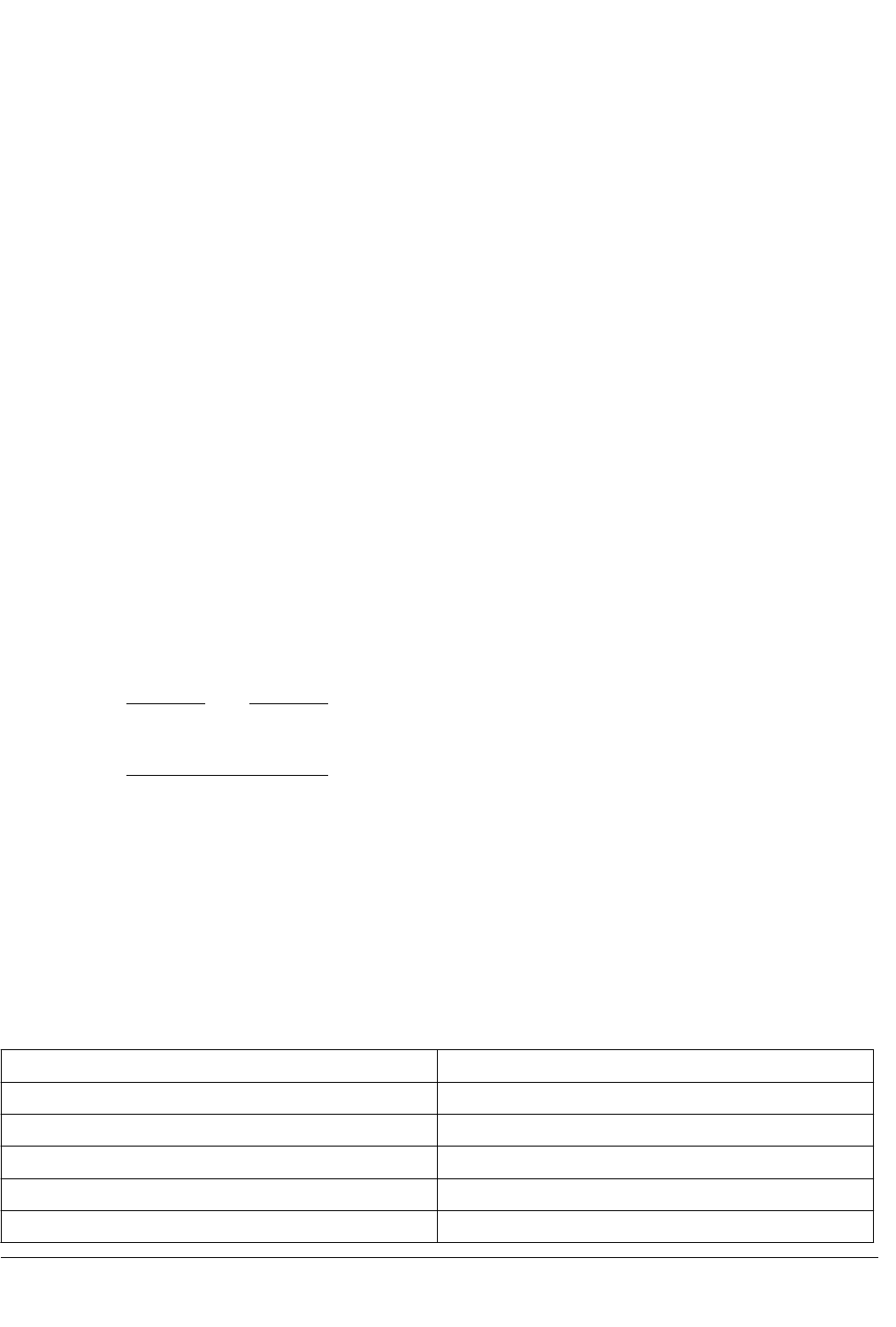

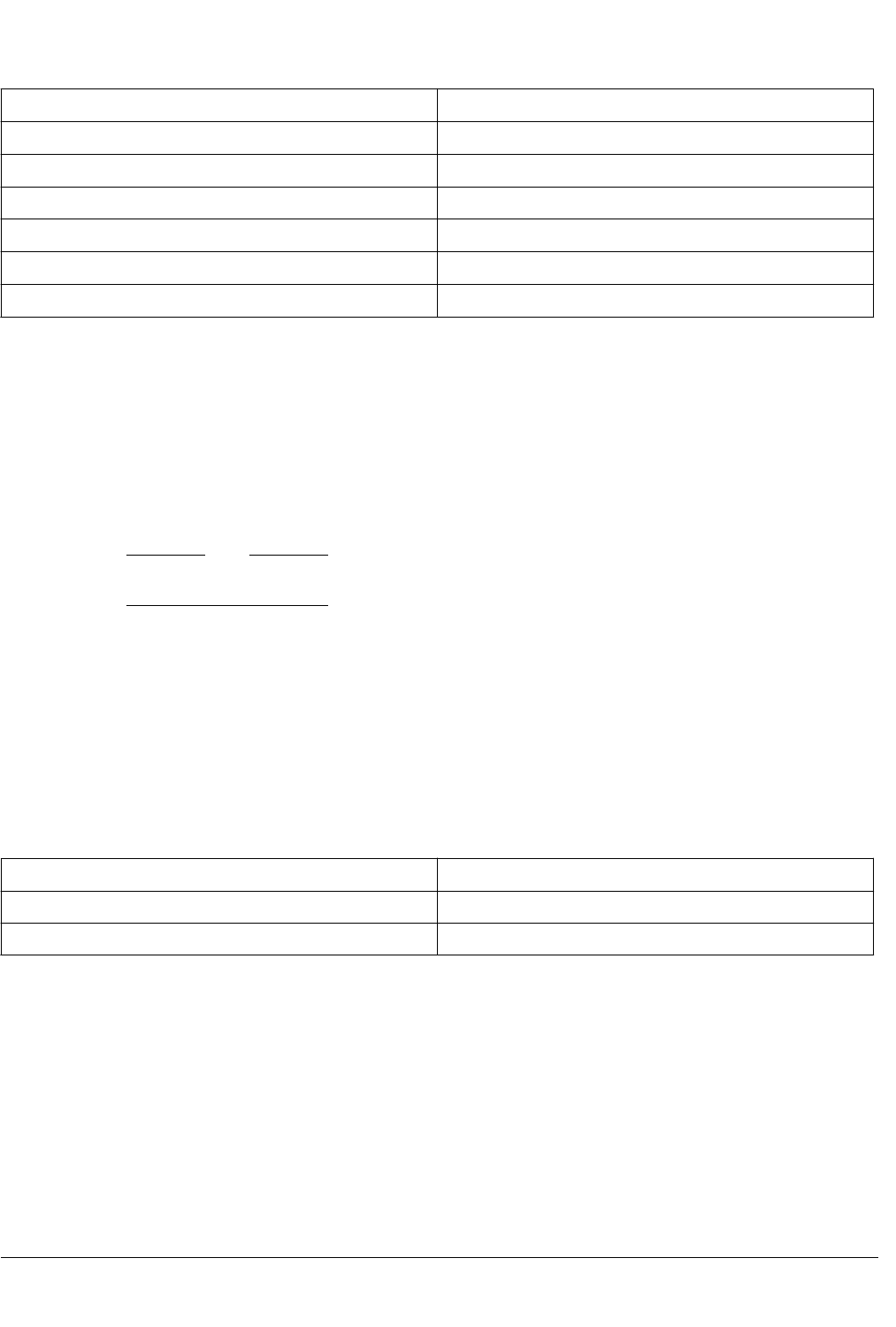

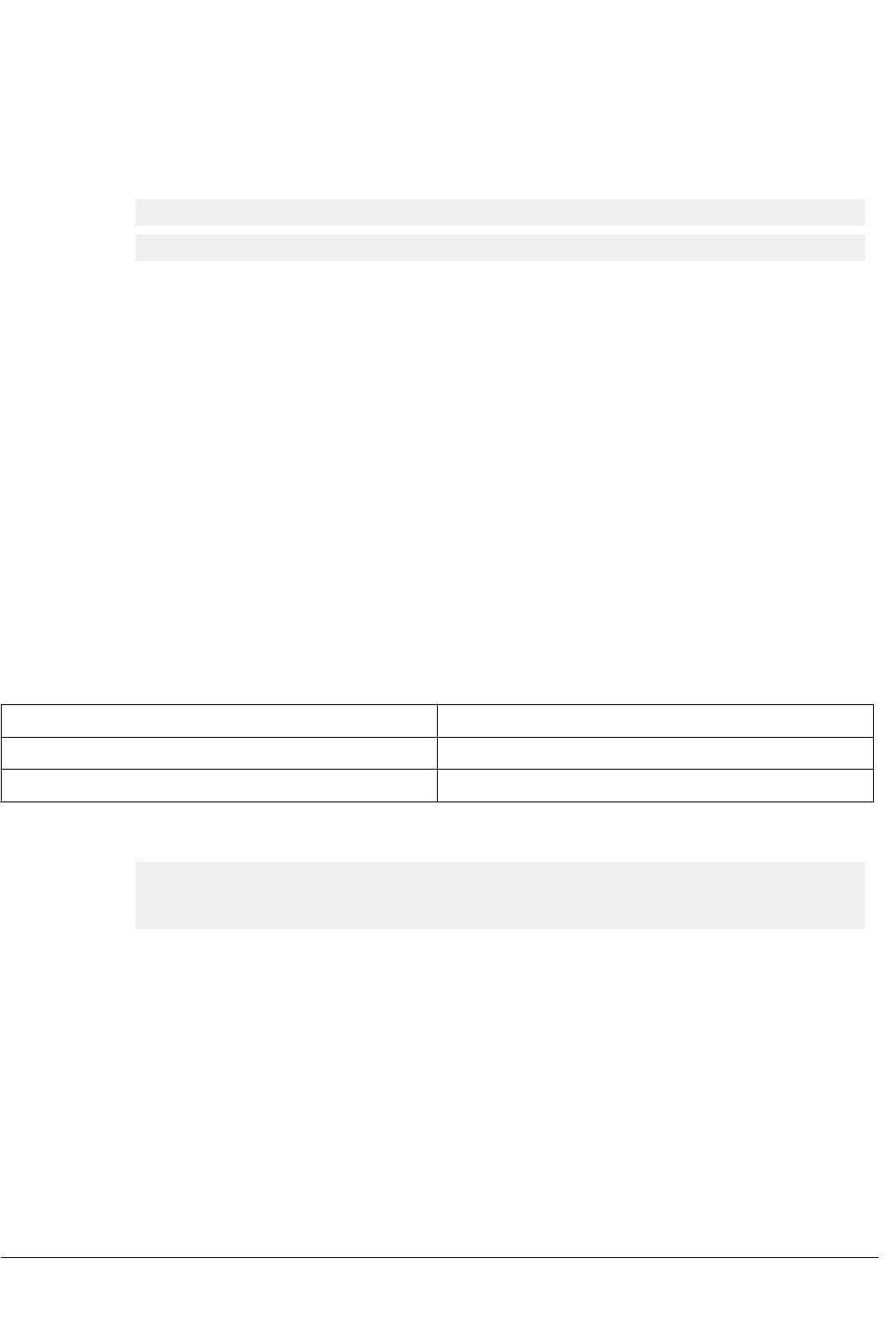

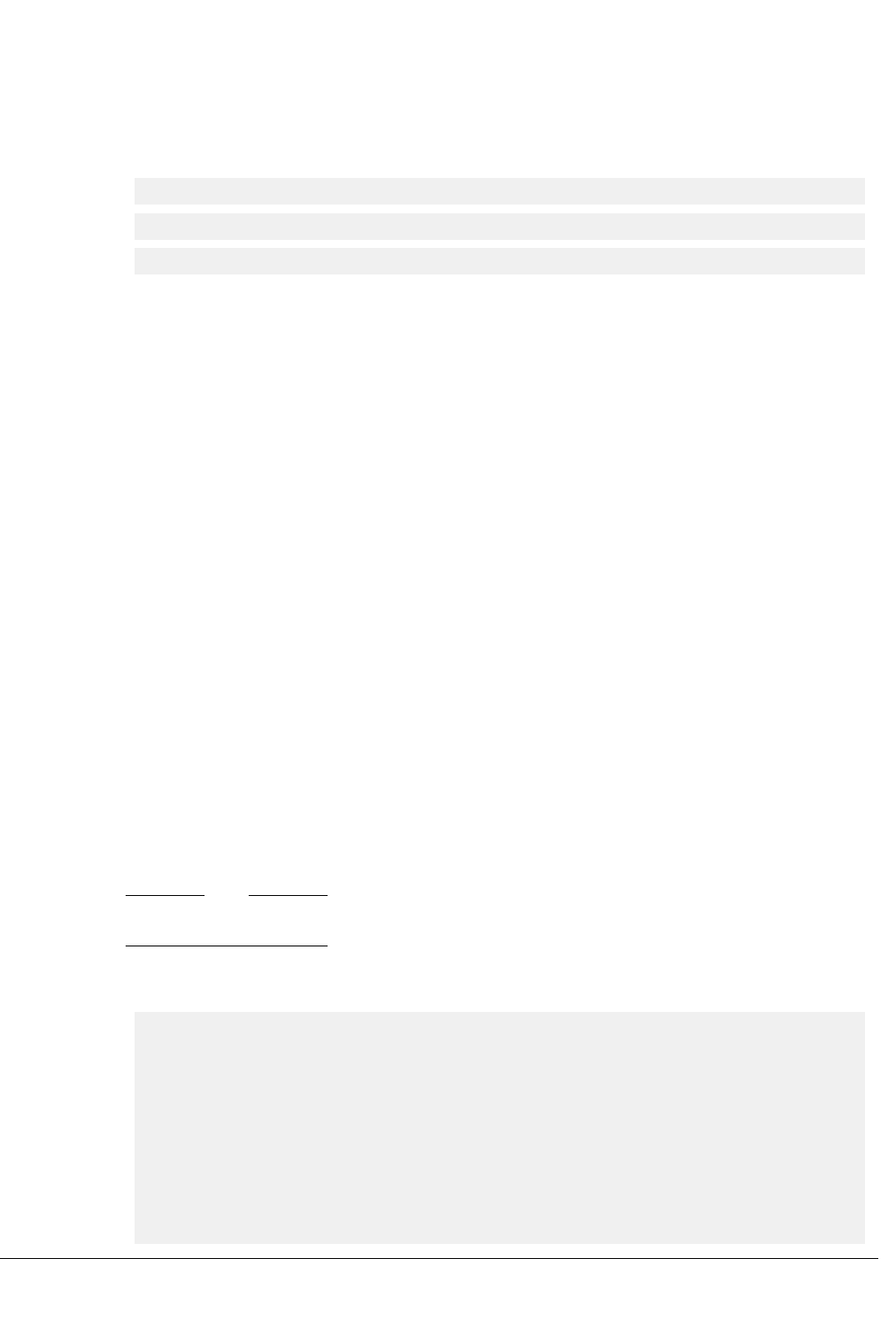

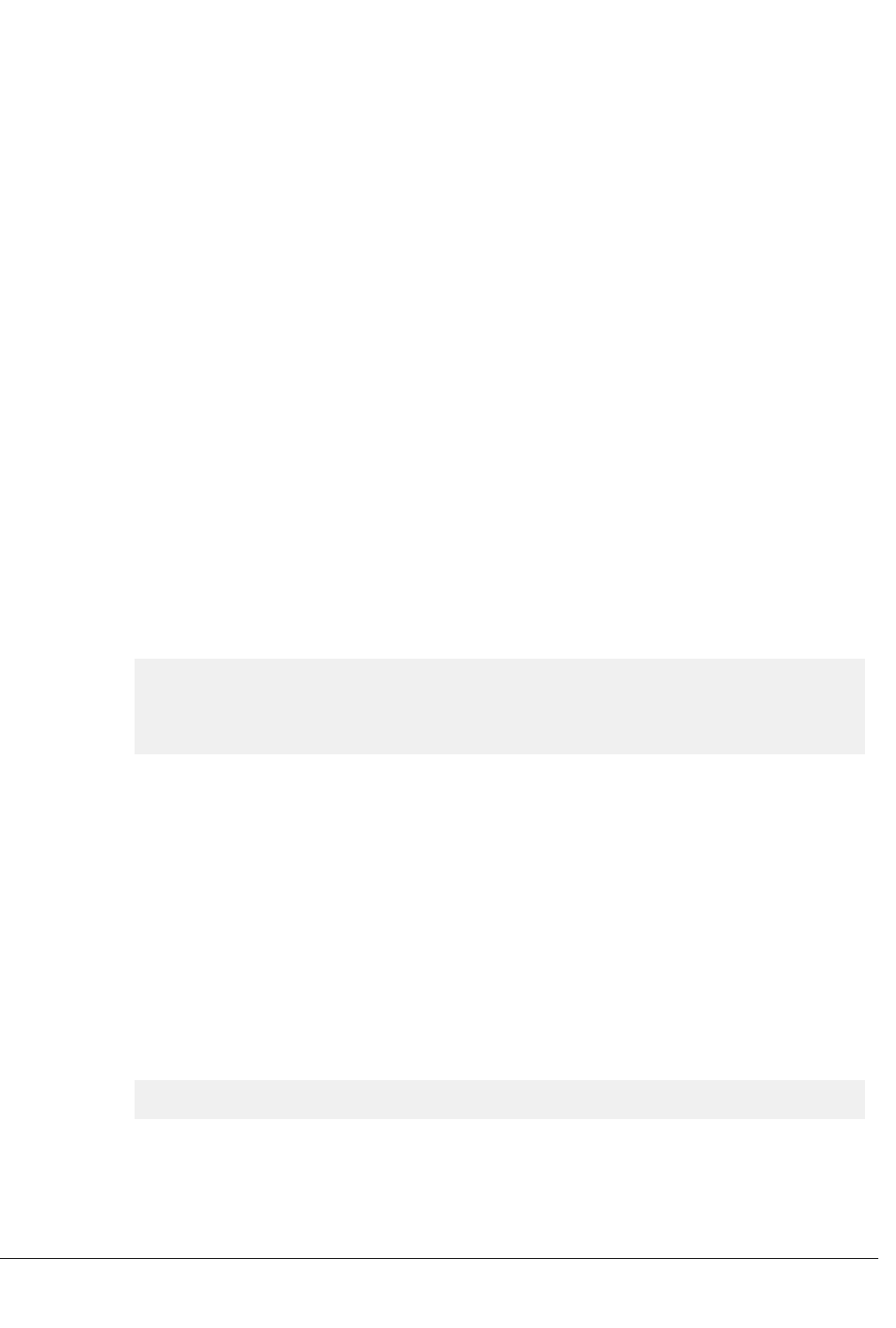

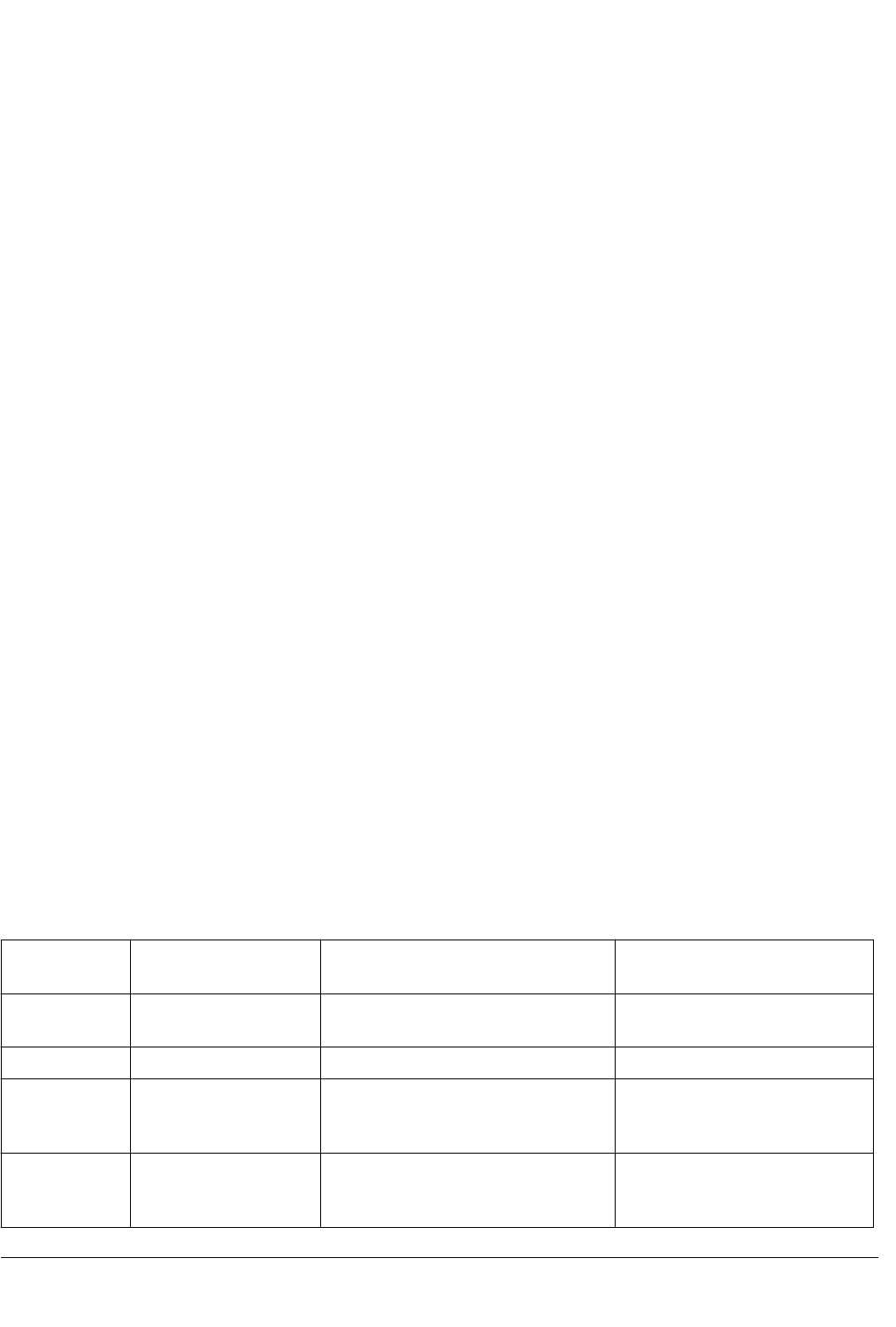

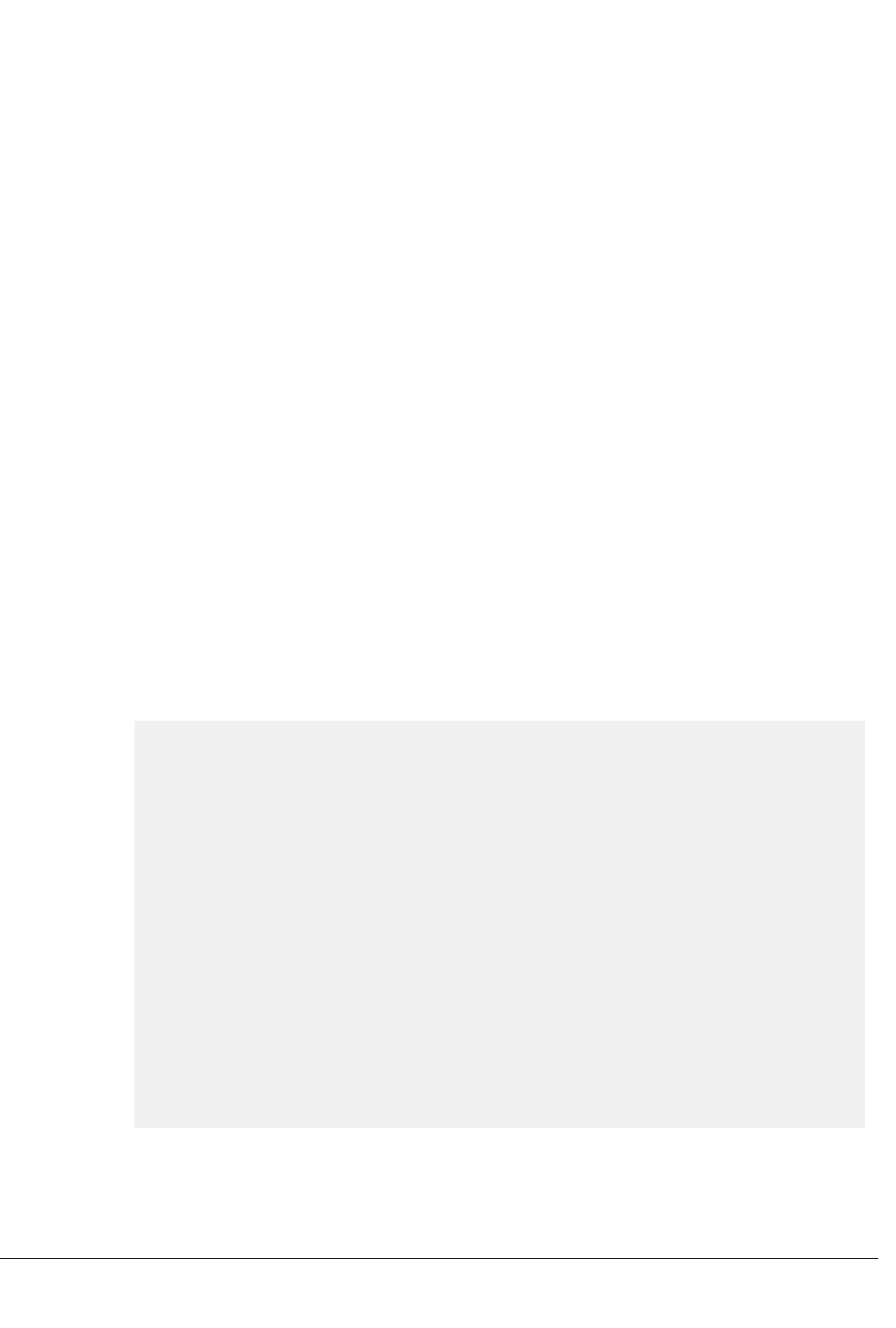

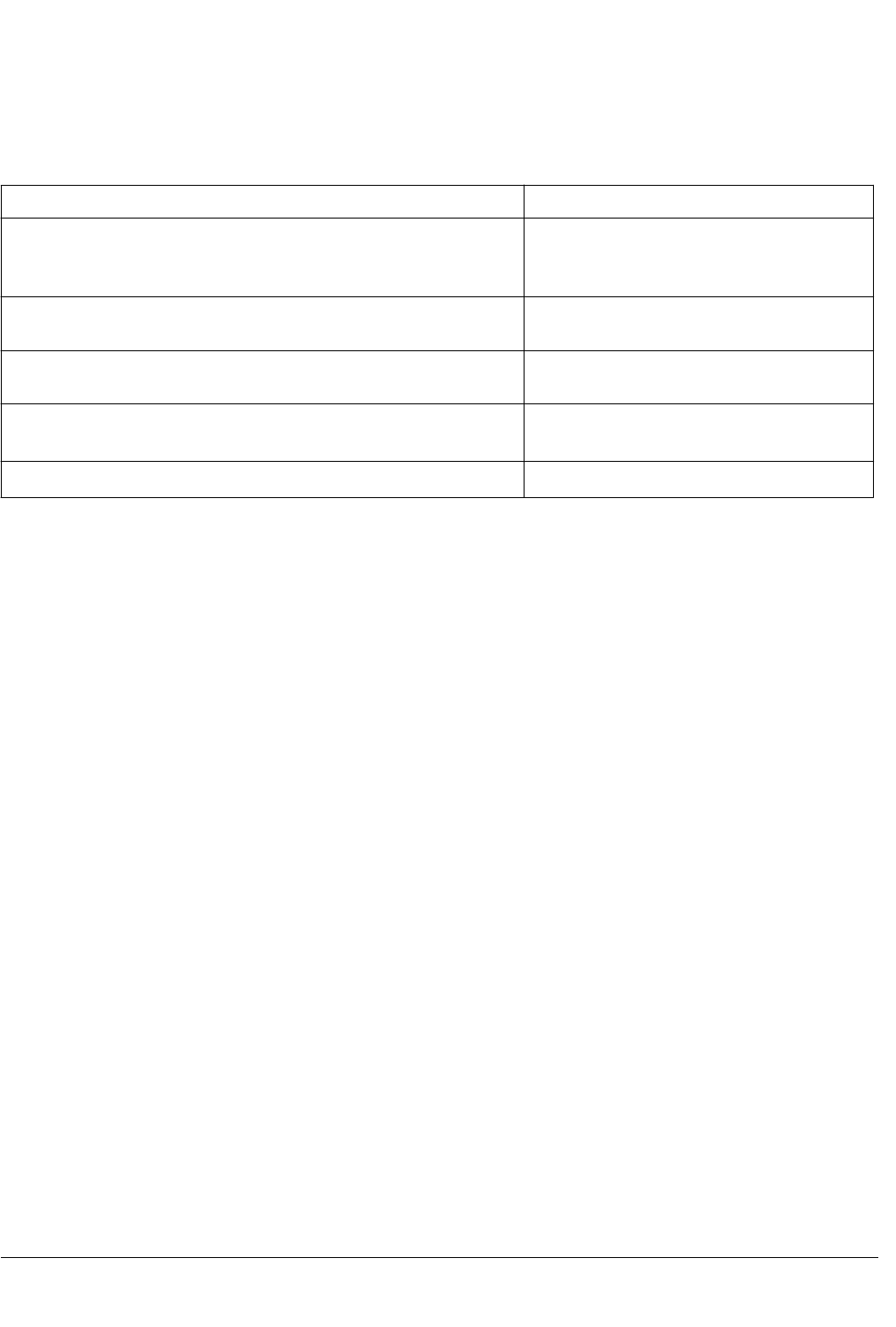

• The following figure shows the structure of the Arm Compiler 6 toolchain:

1 Compiler Command-line Options

1.1 Support level definitions

DUI0774K Copyright © 2014–2017, 2019, 2020 Arm Limited or its affiliates. All

rights reserved.

1-20

Non-Confidential

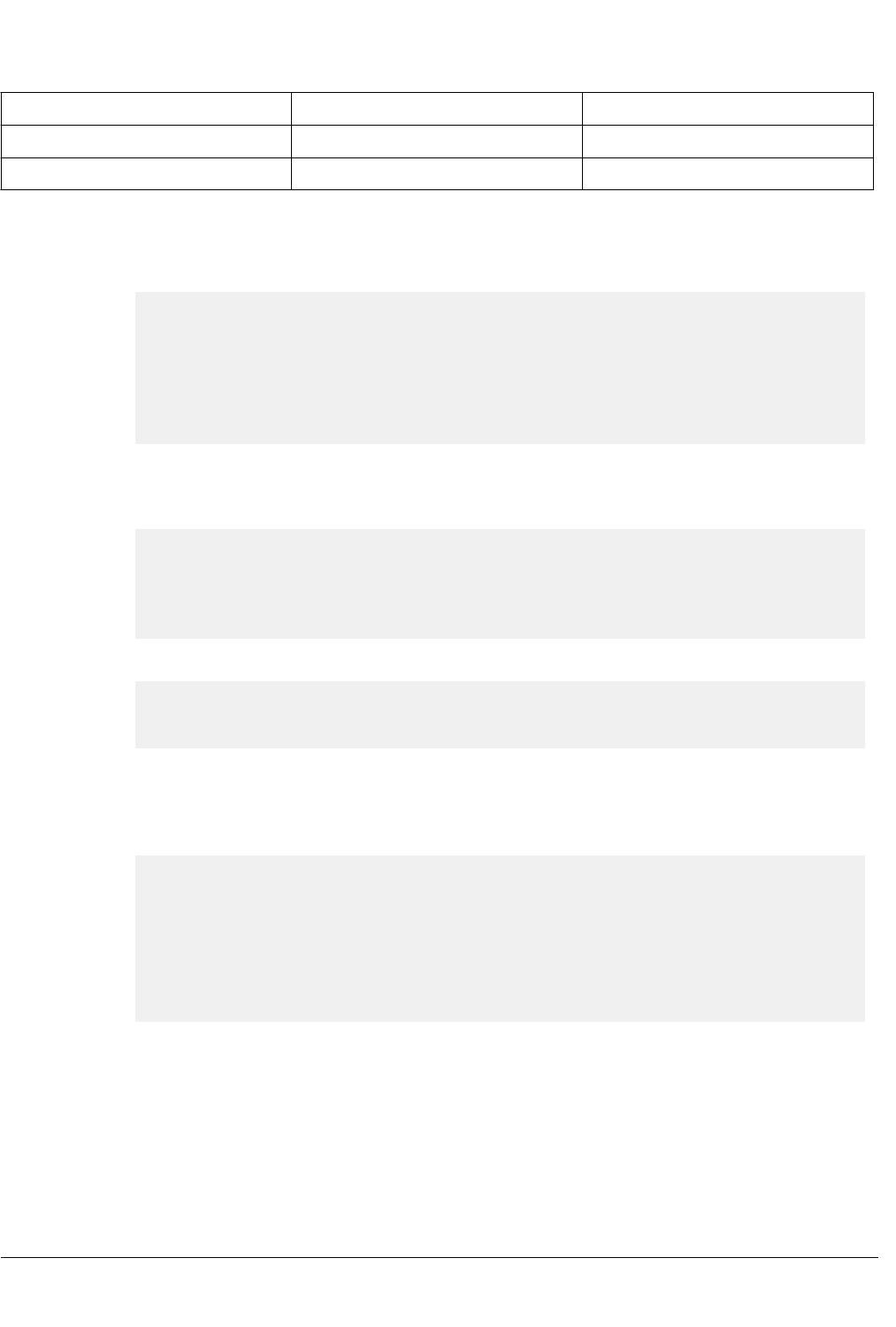

armasm

armclang

Arm C library

Arm C++ library

armlink

LLVM Project

clang

armasm syntax

assembly

armasm syntax

assembly

C/C++

Source code

C/C++

Source code

GNU syntax

Assembly

GNU syntax

Assembly

Source code

headers

Source code

headers

Objects

Objects

Objects

Objects

Objects

Objects

Scatter/Steering/

Symdefs file

Scatter/Steering/

Symdefs file

Image

Image

LLVM Project

libc++

Figure 1-1 Integration boundaries in Arm Compiler 6.

The dashed boxes are toolchain components, and any interaction between these components is an

integration boundary. Community features that span an integration boundary might have significant

limitations in functionality. The exception to this is if the interaction is codified in one of the

standards supported by Arm Compiler 6. See Application Binary Interface (ABI) for the Arm

®

Architecture. Community features that do not span integration boundaries are more likely to work as

expected.

• Features primarily used when targeting hosted environments such as Linux or BSD might have

significant limitations, or might not be applicable, when targeting bare-metal environments.

• The Clang implementations of compiler features, particularly those that have been present for a long

time in other toolchains, are likely to be mature. The functionality of new features, such as support

1 Compiler Command-line Options

1.1 Support level definitions

DUI0774K Copyright © 2014–2017, 2019, 2020 Arm Limited or its affiliates. All

rights reserved.

1-21

Non-Confidential

for new language features, is likely to be less mature and therefore more likely to have limited

functionality.

Unsupported features

With both the product and Community feature categories, specific features and use-cases are known not

to function correctly, or are not intended for use with Arm Compiler 6.

Limitations of product features are stated in the documentation. Arm cannot provide an exhaustive list of

unsupported features or use-cases for Community features. The known limitations on Community

features are listed in Community features on page 1-19.

List of known unsupported features

The following is an incomplete list of unsupported features, and might change over time:

• The Clang option -stdlib=libstdc++ is not supported.

• C++ static initialization of local variables is not thread-safe when linked against the standard C++

libraries. For thread-safety, you must provide your own implementation of thread-safe functions as

described in Standard C++ library implementation definition.

Note

This restriction does not apply to the [ALPHA]-supported multi-threaded C++ libraries.

• Use of C11 library features is unsupported.

• Any Community feature that exclusively pertains to non-Arm architectures is not supported.

• Compilation for targets that implement architectures older than Armv7 or Armv6‑M is not supported.

• The long double data type is not supported for AArch64 state because of limitations in the current

Arm C library.

• Complex numbers are not supported because of limitations in the current Arm C library.

1 Compiler Command-line Options

1.1 Support level definitions

DUI0774K Copyright © 2014–2017, 2019, 2020 Arm Limited or its affiliates. All

rights reserved.

1-22

Non-Confidential

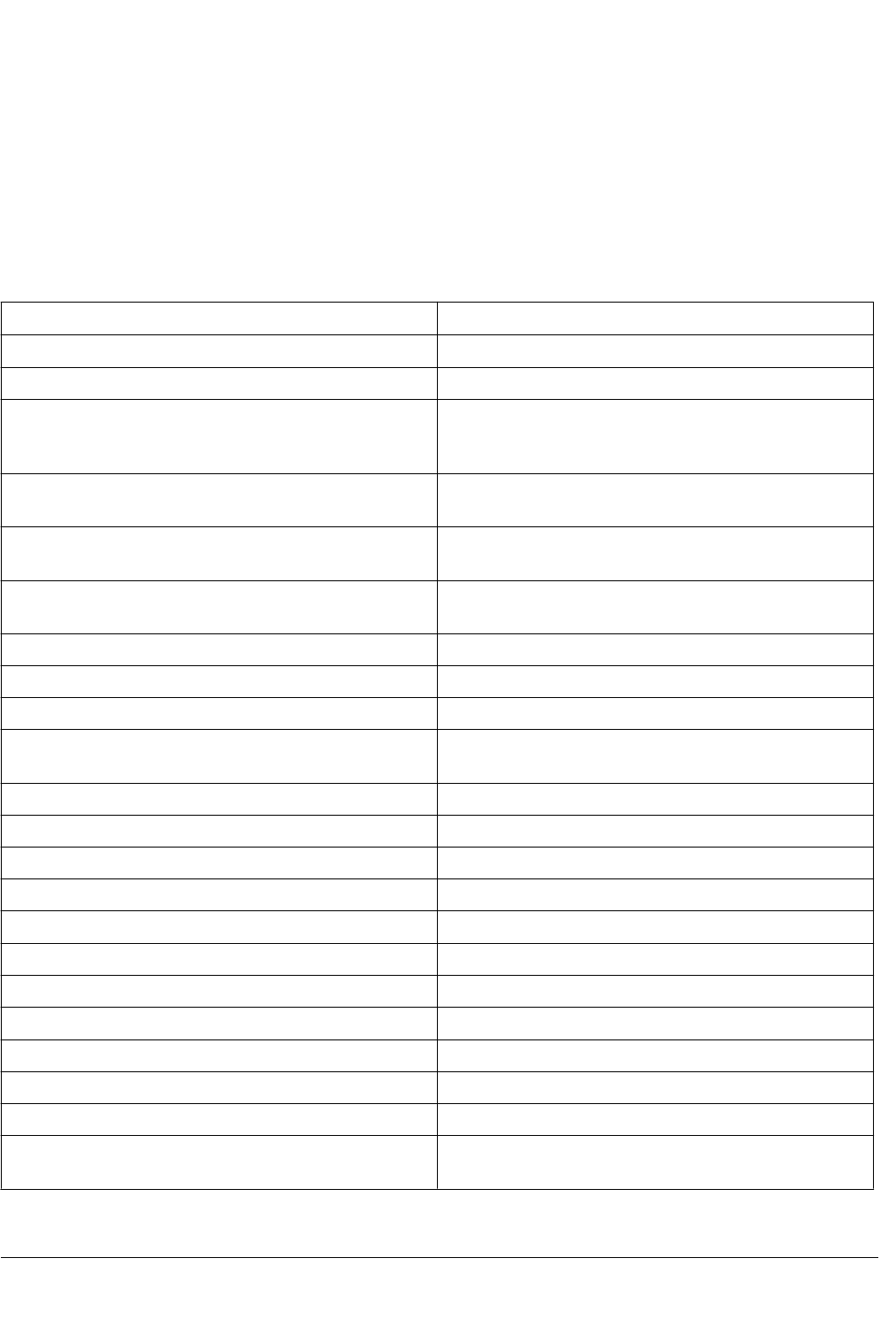

1.2 Summary of armclang command-line options

This provides a summary of the armclang command-line options that Arm Compiler 6 supports.

The command-line options either affect both compilation and assembly, or only affect compilation. The

command-line options that only affect compilation without affecting armclang integrated assembler are

shown in the table as Compilation only. The command-line options that affect both compilation and

assembly are shown in the table as Compilation and assembly.

Note

The command-line options that affect assembly are for the armclang integrated assembler, and do not

apply to armasm. These options affect both inline assembly and assembly language source files.

Note

Assembly language source files are assembled using the armclang integrated assembler. C and C++

language source files, which can contain inline assembly code, are compiled using the armclang

compiler. Command-line options that are shown as Compilation only do not affect the integrated

assembler, but they can affect inline assembly code.

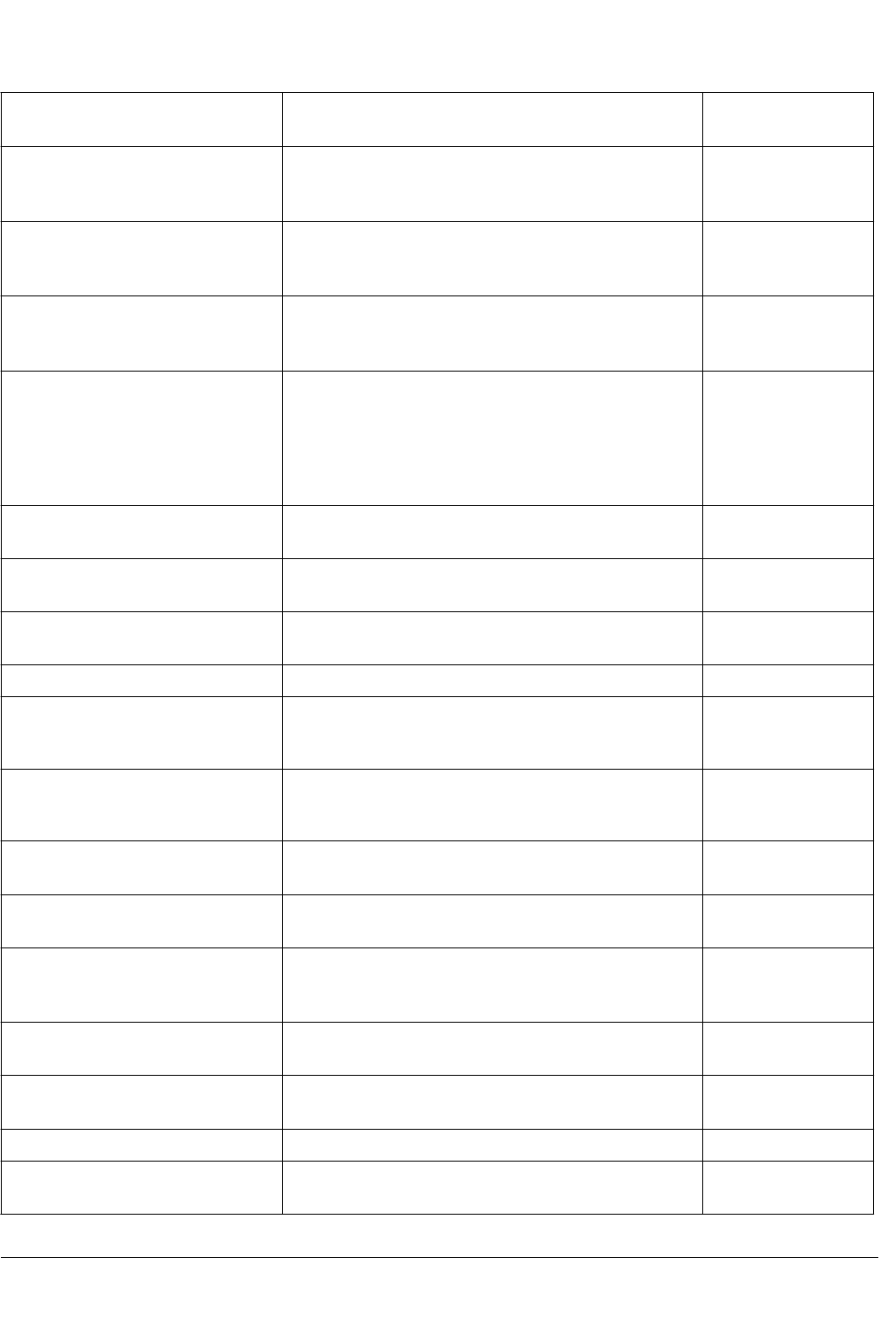

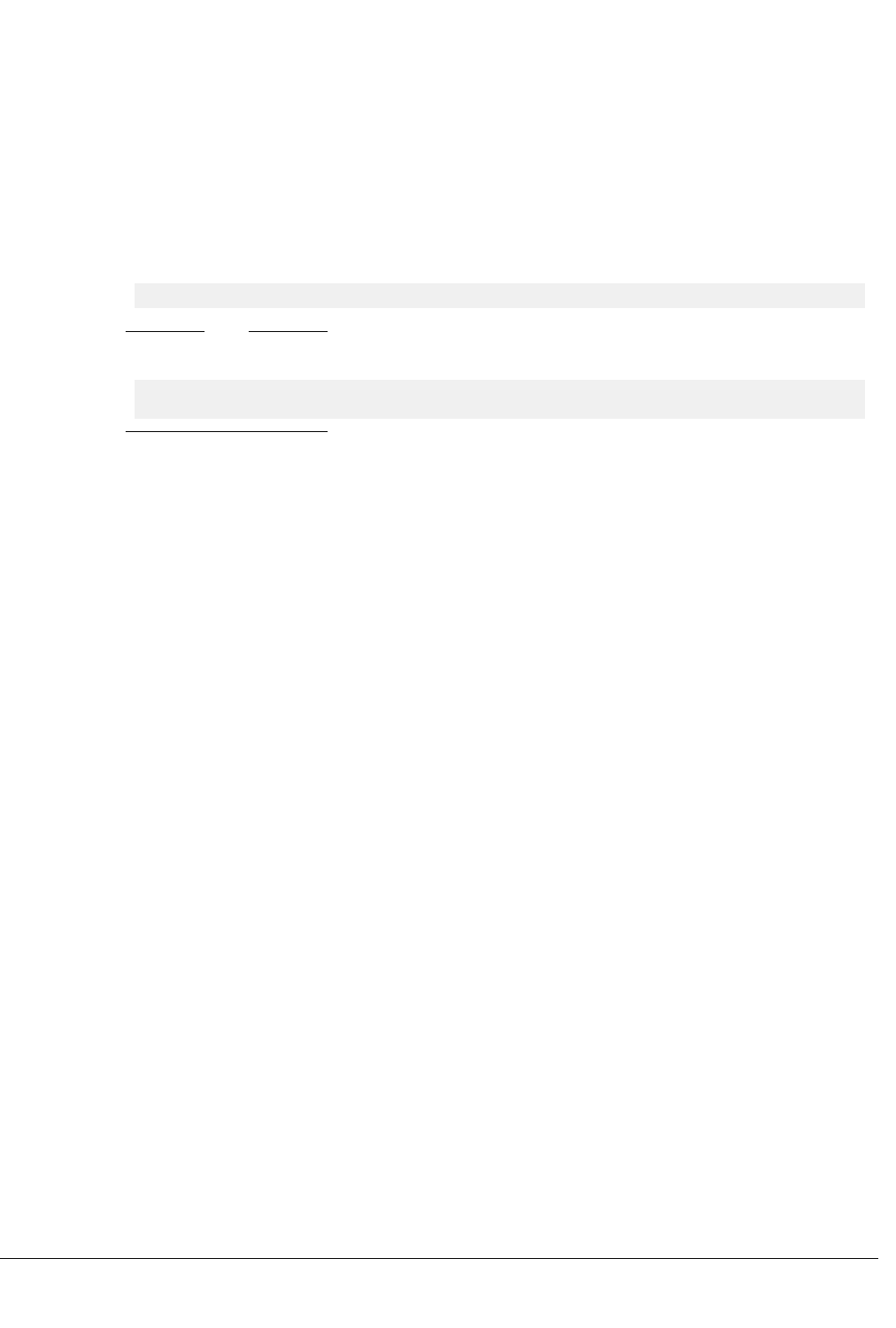

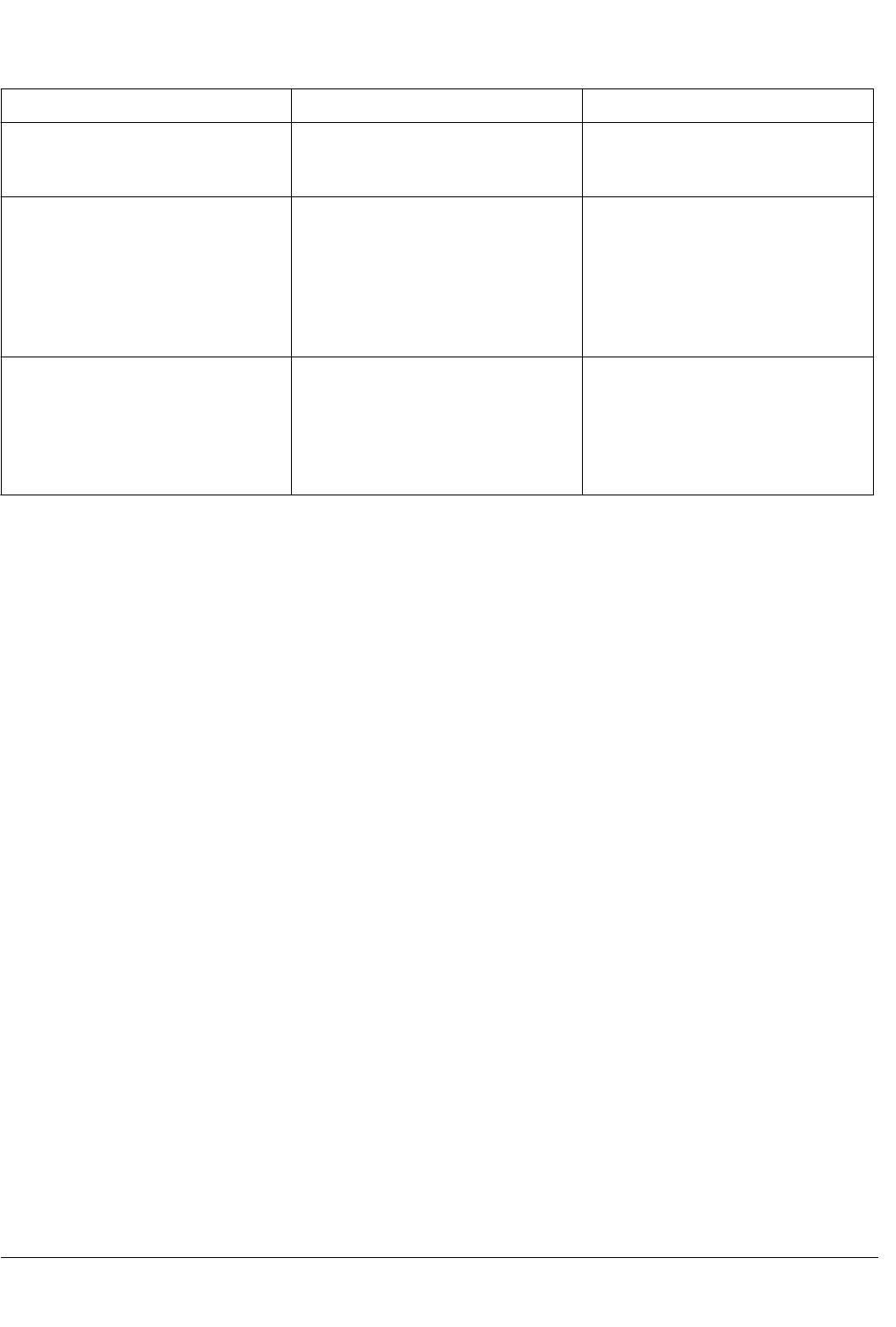

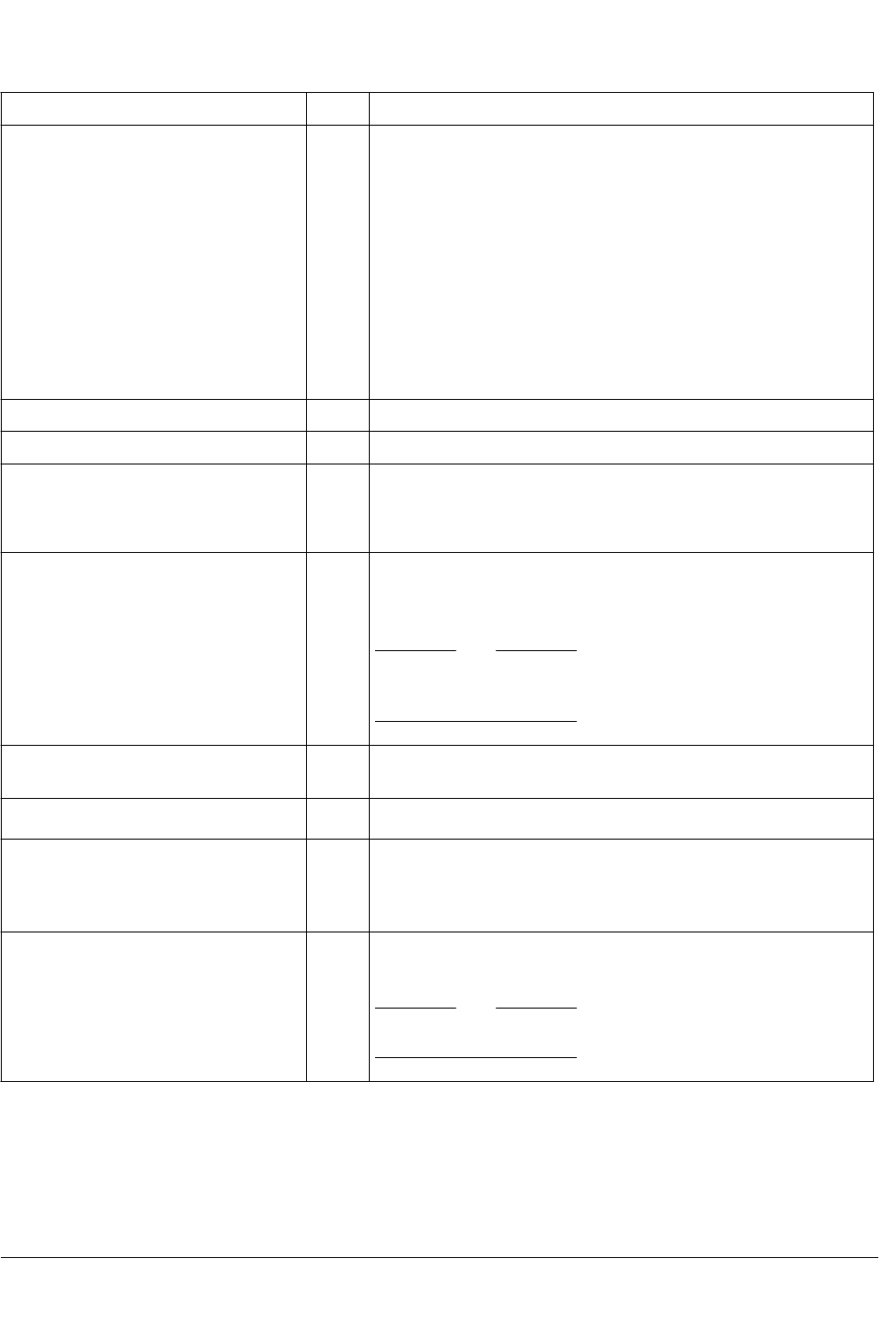

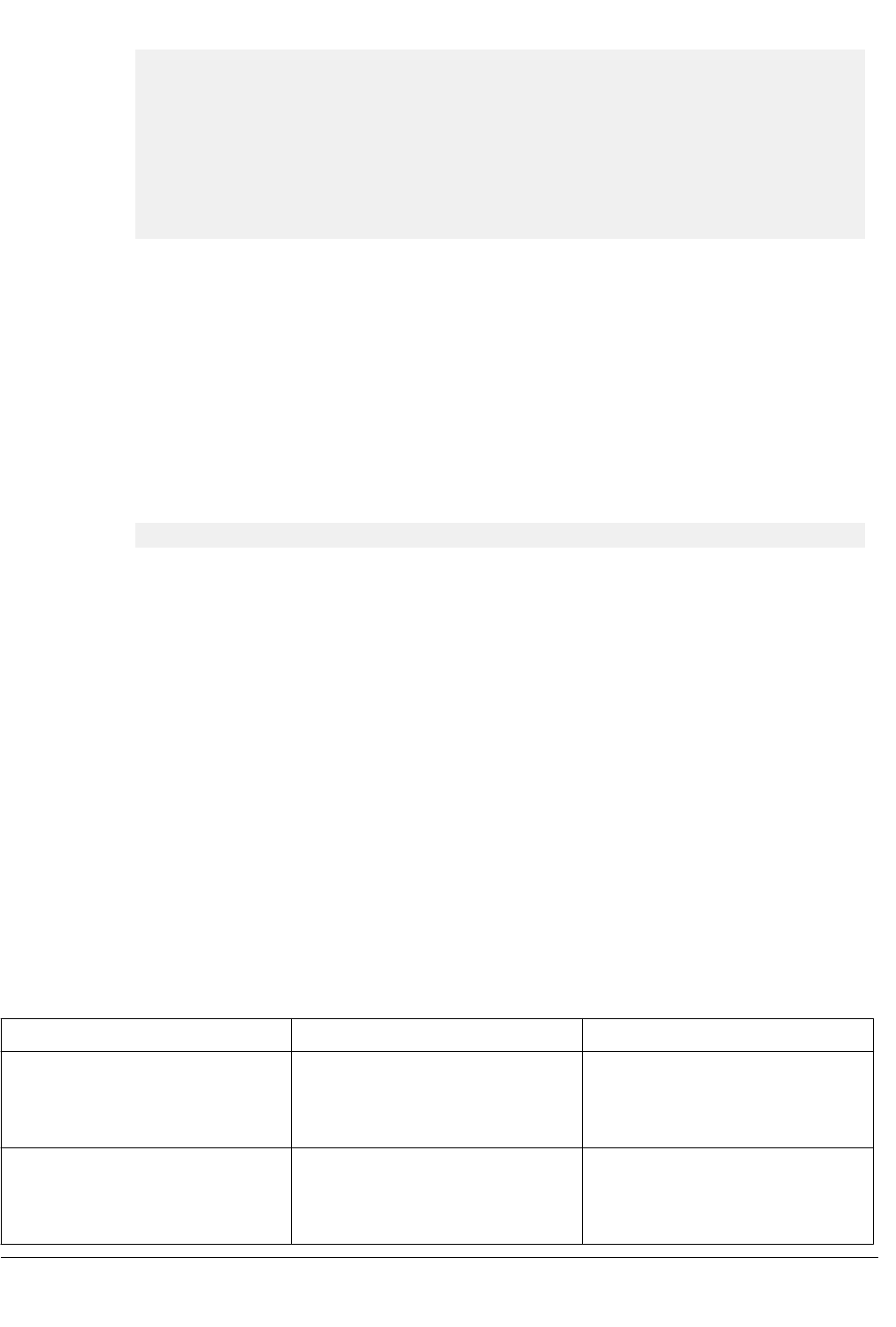

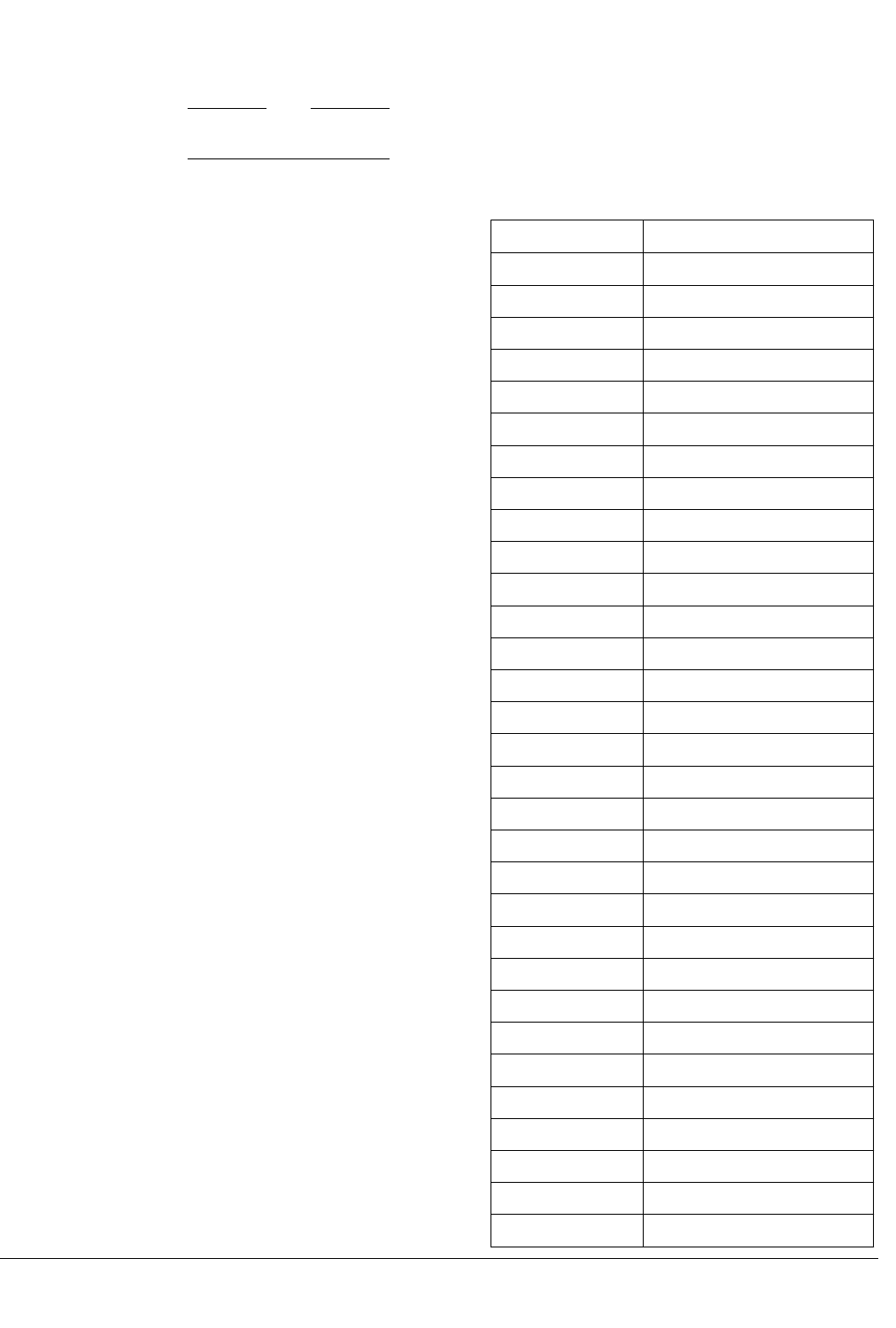

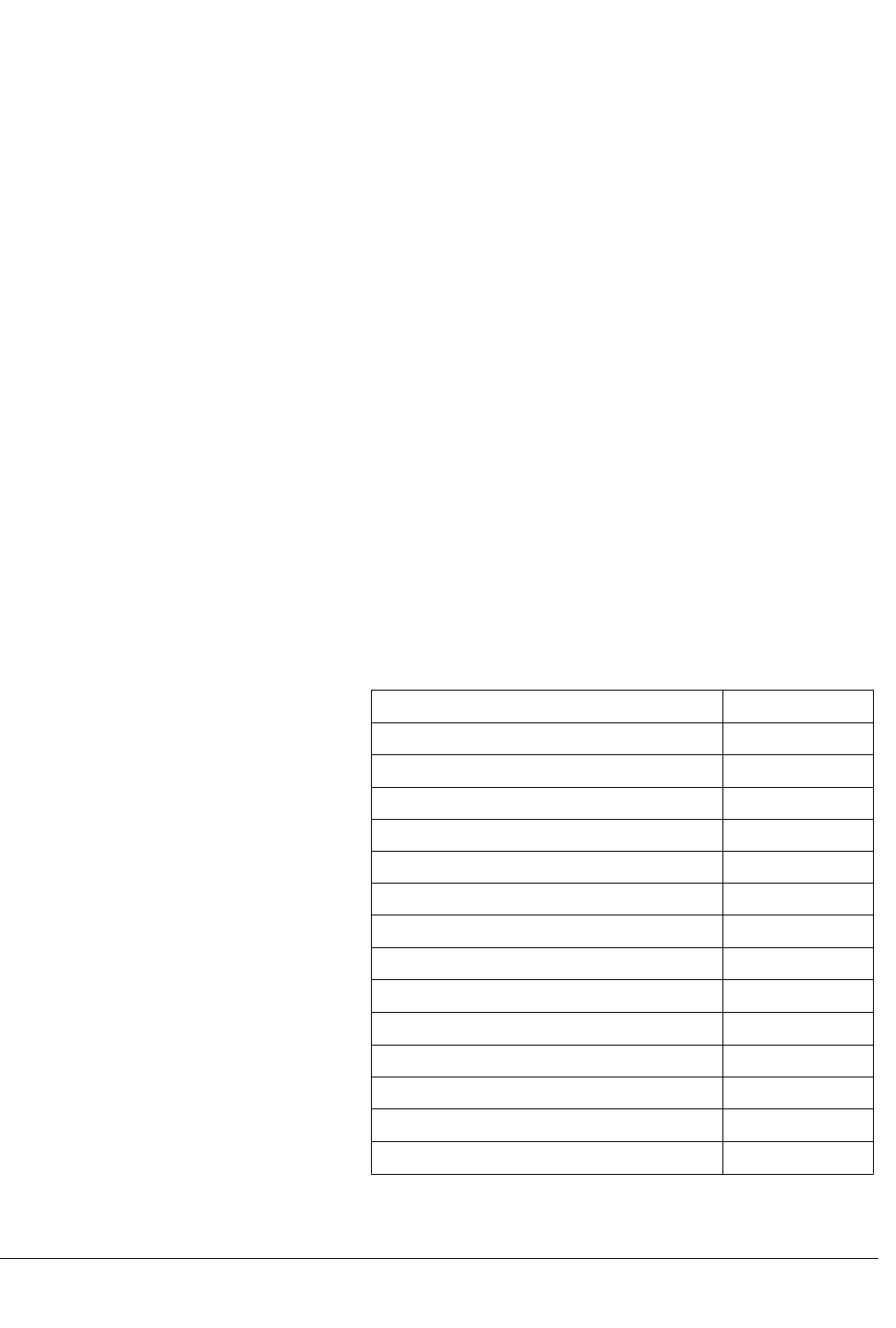

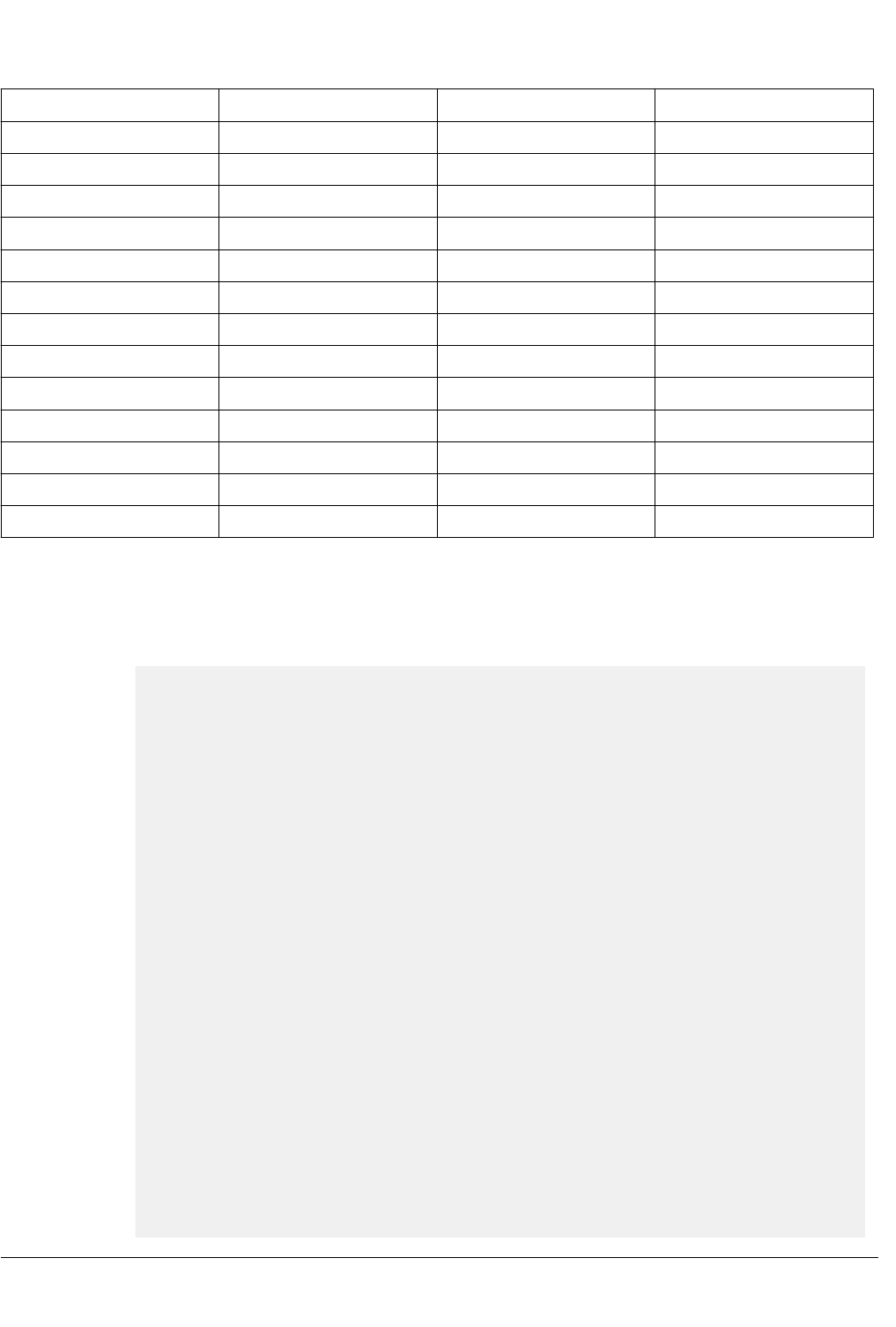

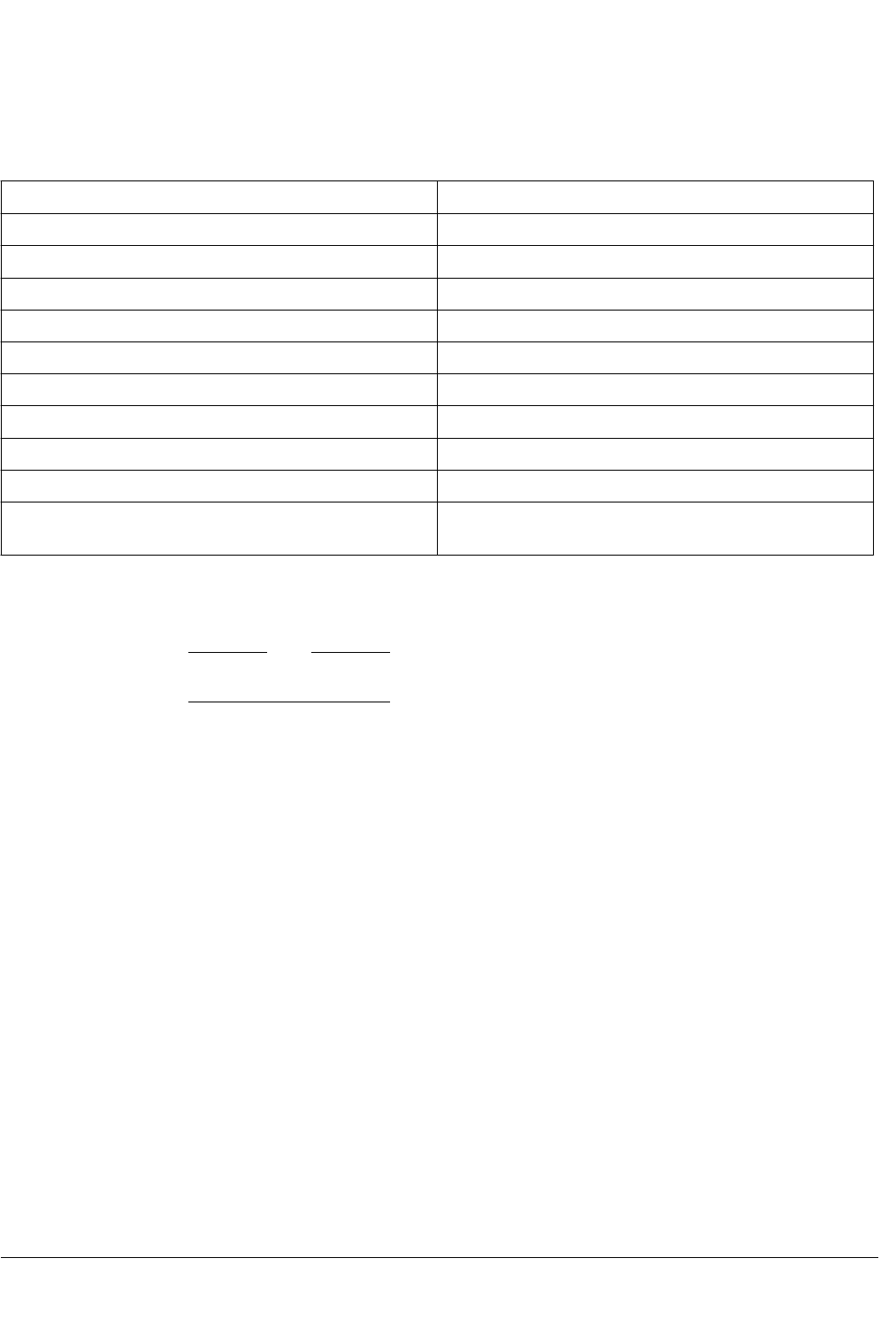

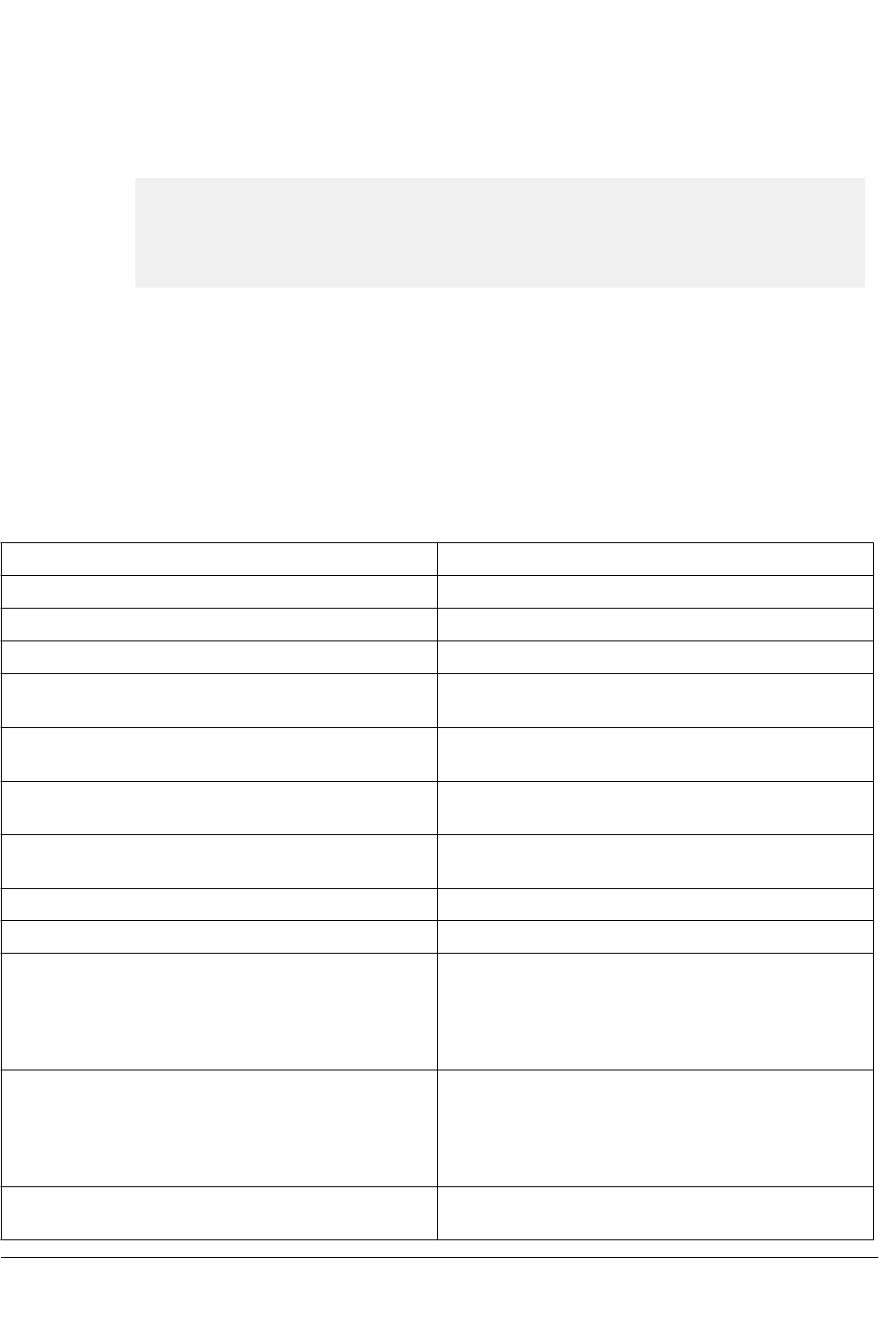

Table 1-1 armclang command-line options

Option Description Compilation or

Assembly

-c

Only perform the compile step, do not invoke armlink. Compilation and

assembly.

-D

Defines a preprocessor macro. Compilation and

assembly.

-E

Only perform the preprocess step, do not compile or link. Compilation and

assembly.

-e

Specifies the unique initial entry point of the image. Compilation and

assembly.

-fbare-metal-pie

Generates position-independent code. Compilation only.

-fbracket-depth

Sets the limit for nested parentheses, brackets, and braces. Compilation and

assembly.

-fcommon,

-fno-common

Generates common zero-initialized values for tentative

definitions.

Compilation only.

-fdata-sections,

-fno-data-sections

Enables or disables the generation of one ELF section for each

variable in the source file.

Compilation only.

-ffast-math,

-fno-fast-math

Enables or disables the use of aggressive floating-point

optimizations.

Compilation only.

-ffp-mode

Specifies floating-point standard conformance. Compilation only.

-ffunction-sections,

-fno-function-sections

Enables or disables the generation of one ELF section for each

function in the source file.

Compilation only.

1 Compiler Command-line Options

1.2 Summary of armclang command-line options

DUI0774K Copyright © 2014–2017, 2019, 2020 Arm Limited or its affiliates. All

rights reserved.

1-23

Non-Confidential

Table 1-1 armclang command-line options (continued)

Option Description Compilation or

Assembly

@file

Reads a list of command-line options from a file. Compilation and

assembly.

-fldm-stm,

-fno-ldm-stm

Enable or disable the generation of LDM and STM instructions.

AArch32 only.

Compilation only.

-fno-inline-functions

Disables the automatic inlining of functions at optimization

levels -O2 and -O3.

Compilation only.

-flto

Enables link time optimization, and outputs bitcode wrapped in

an ELF file for link time optimization.

Compilation only.

-fexceptions,

-fno-exceptions

Enables or disables the generation of code needed to support C

++ exceptions.

Compilation only.

-fomit-frame-pointer,

-fno-omit-frame-pointer

Enables or disables the storage of stack frame pointers during

function calls.

Compilation only.

-fno-builtin

Disables special handling and optimizations of standard C

library functions.

Compilation only.

-fropi,

-fno-ropi

Enables or disables the generation of Read-Only Position-

Independent (ROPI) code.

Compilation only.

-fropi-lowering,

-fno-ropi-lowering

Enables or disables runtime static initialization when

generating Read-Only Position-Independent (ROPI) code.

Compilation only.

-frwpi,

-fno-rwpi

Enables or disables the generation of Read-Write Position-

Independent (RWPI) code.

Compilation only.

-frwpi-lowering,

-fno-rwpi-lowering

Enables or disables runtime static initialization when

generating Read-Write Position-Independent (RWPI) code.

Compilation only.

-fshort-enums,

-fno-short-enums

Allows or disallows the compiler to set the size of an

enumeration type to the smallest data type that can hold all

enumerator values.

Compilation only.

-fshort-wchar,

-fno-short-wchar

Sets the size of wchar_t to 2 or 4 bytes. Compilation only.

-fstack-protector,

-fstack-protector-strong,

-fstack-protector-all,

-fno-stack-protector

Inserts a guard variable onto the stack frame for each

vulnerable function or for all functions.

Compilation only.

-fstrict-aliasing,

-fno-strict-aliasing

Instructs the compiler to apply or not apply the strictest aliasing

rules available.

Compilation only.

1 Compiler Command-line Options

1.2 Summary of armclang command-line options

DUI0774K Copyright © 2014–2017, 2019, 2020 Arm Limited or its affiliates. All

rights reserved.

1-24

Non-Confidential

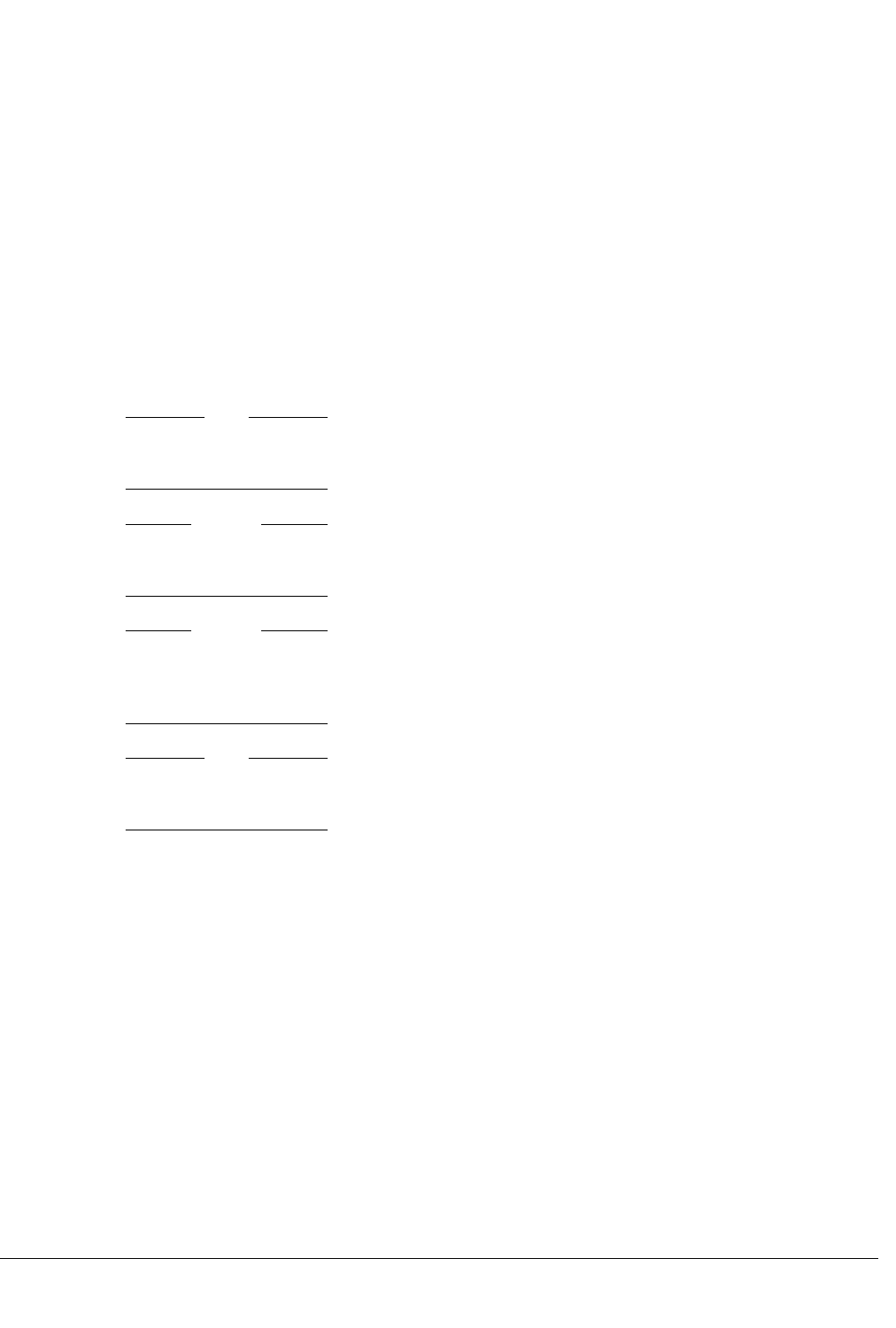

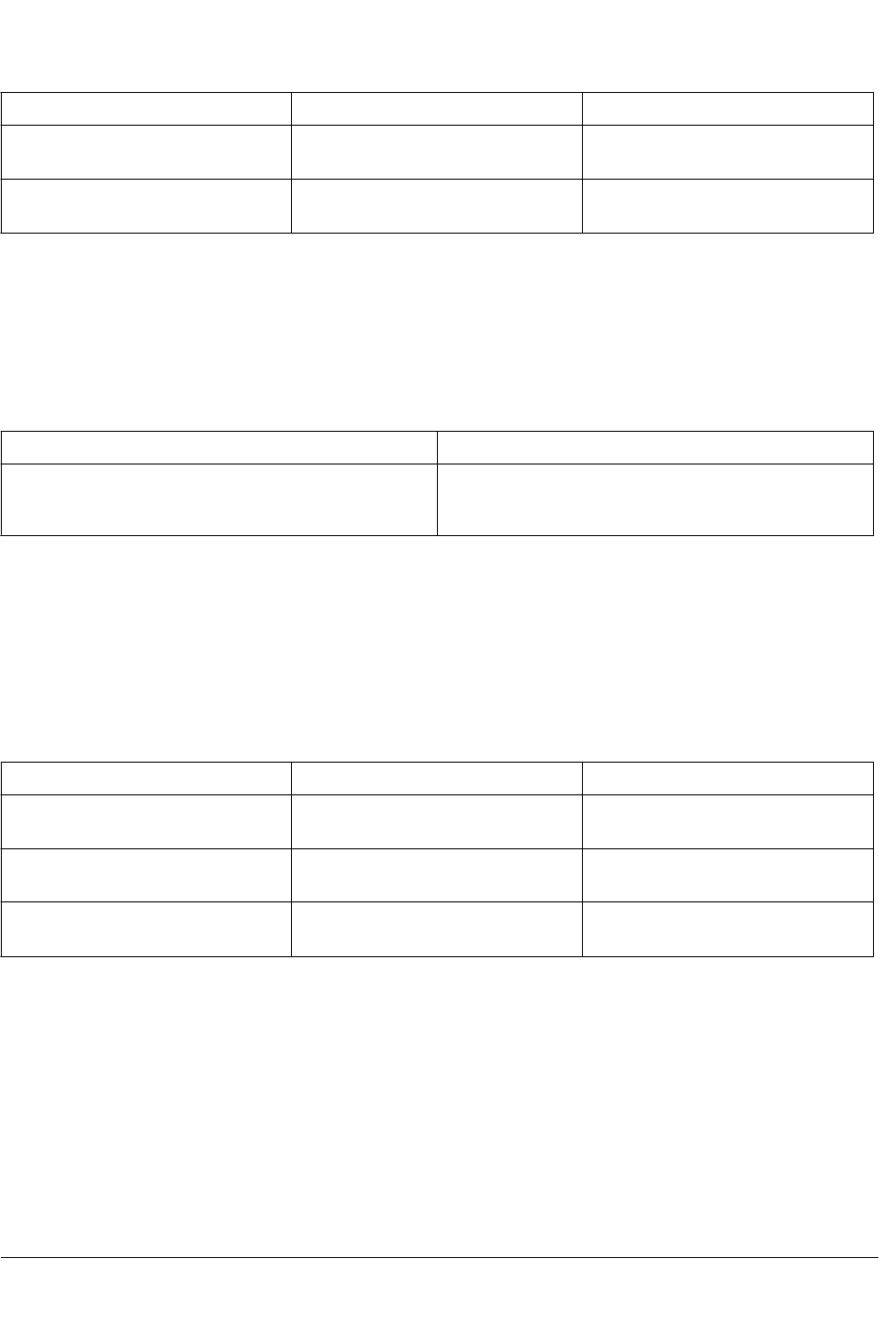

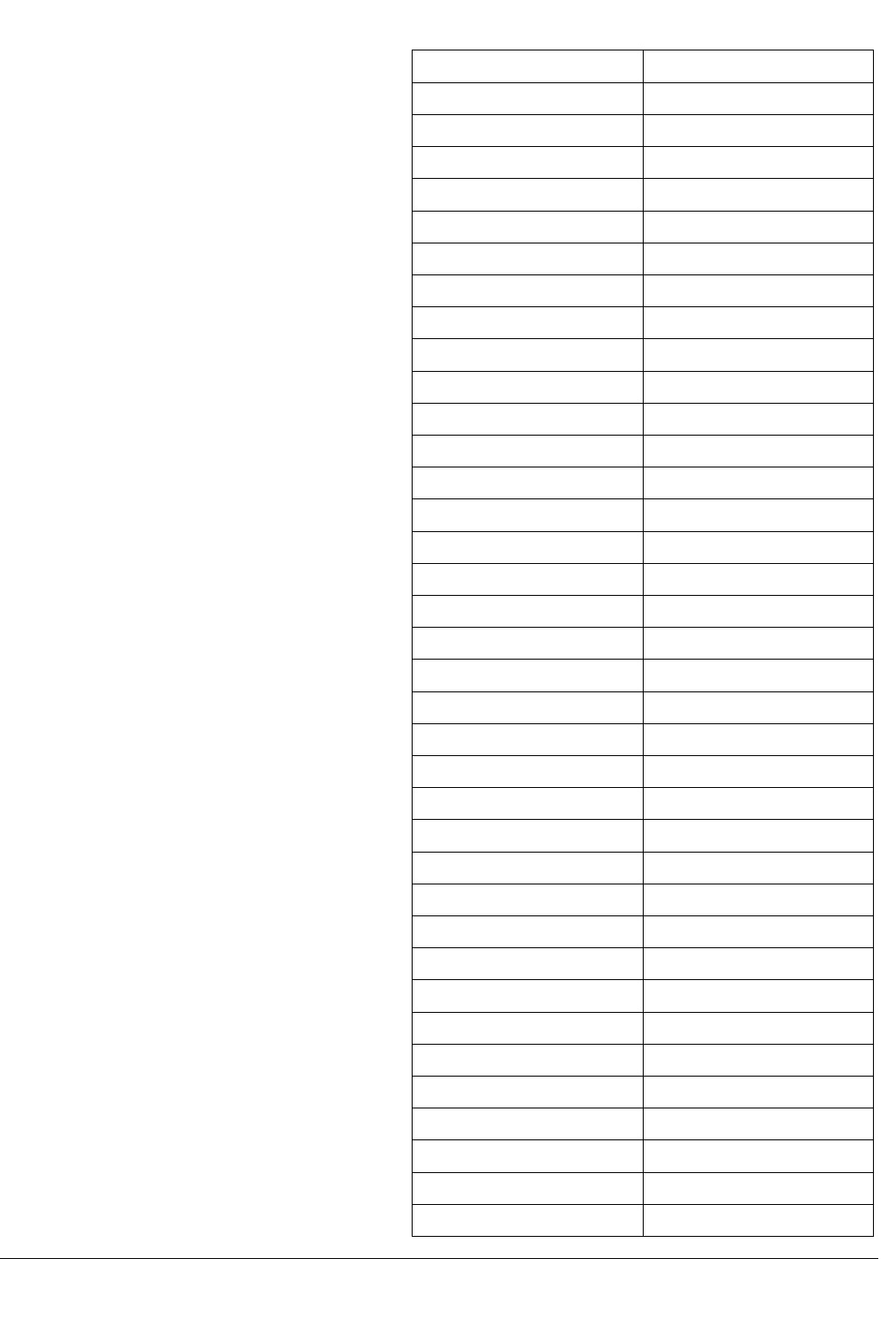

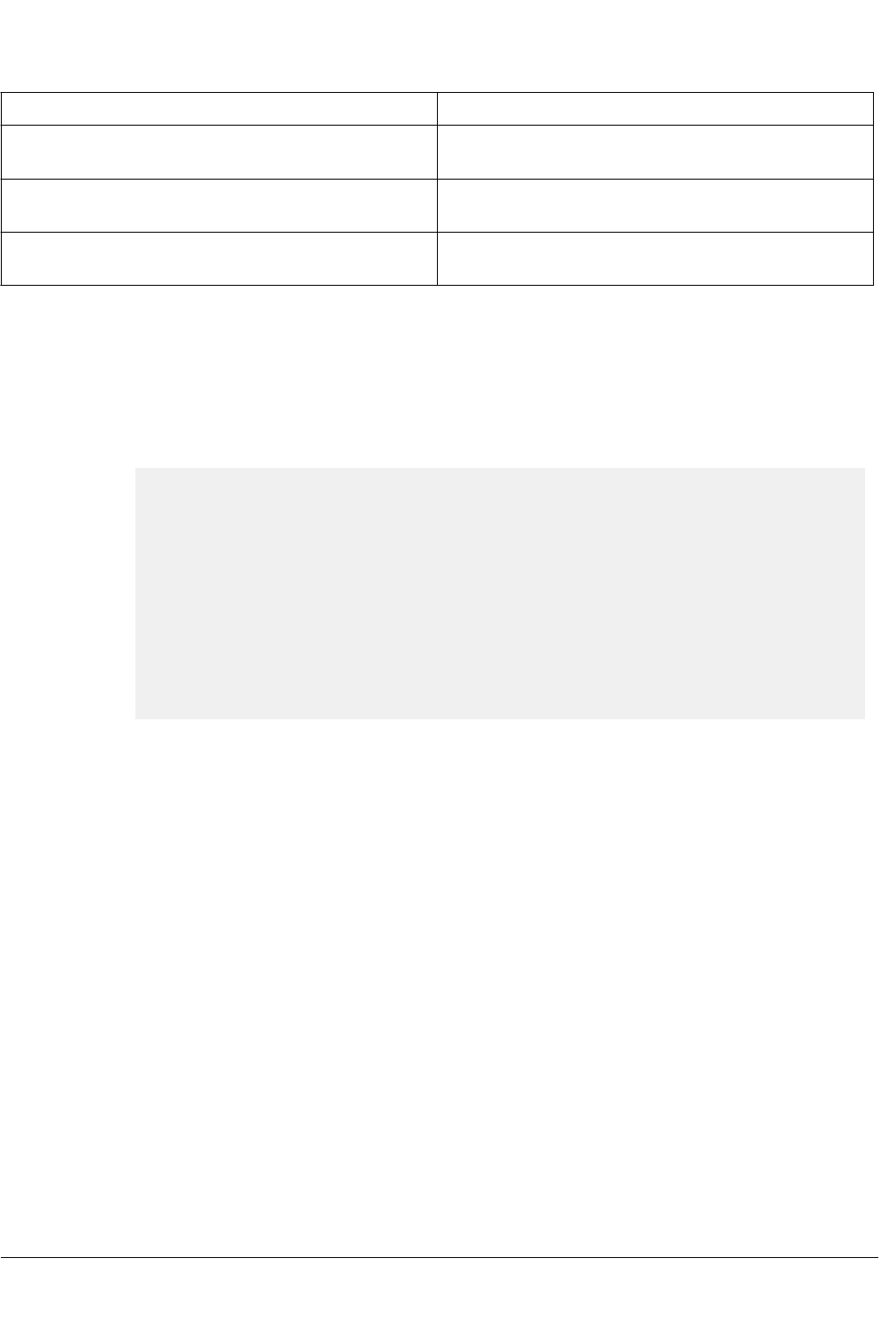

Table 1-1 armclang command-line options (continued)

Option Description Compilation or

Assembly

-fvectorize,

-fno-vectorize

Enables or disables the generation of Advanced SIMD vector

instructions directly from C or C++ code at optimization levels

-O1 and higher.

Compilation only.

-ftrapv

Instructs the compiler to generate traps for signed arithmetic

overflow on addition, subtraction, and multiplication

operations.

Compilation only.

-fwrapv

Instructs the compiler to assume that signed arithmetic

overflow of addition, subtraction, and multiplication, wraps

using two's-complement representation.

Compilation only.

-g,

-gdwarf-2,

-gdwarf-3,

-gdwarf-4

Adds debug tables for source-level debugging. Compilation and

assembly.

-I

Adds the specified directory to the list of places that are

searched to find include files.

Compilation and

assembly.

-include

Includes the source code of the specified file at the beginning of

the compilation.

Compilation only.

-L

Specifies a list of paths that the linker searches for user

libraries.

Compilation only.

-l

Add the specified library to the list of searched libraries. Compilation only.

-M,

-MM

Produces a list of makefile dependency rules suitable for use by

a make utility.

Compilation and

assembly.

-MD,

-MMD

Compiles or assembles source files and produces a list of

makefile dependency rules suitable for use by a make utility.

Compilation and

assembly.

-MF

Specifies a filename for the makefile dependency rules

produced by the -M and -MD options.

Compilation only.

-MG

Prints dependency lines for header files even if the header files

are missing.

Compilation only.

-MP

Emits dummy dependency rules that work around make errors

that are generated if you remove header files without a

corresponding update to the makefile.

Compilation only.

-MT

Changes the target of the makefile dependency rule produced

by dependency generating options.

Compilation and

assembly.

-march

Targets an architecture profile, generating generic code that

runs on any processor of that architecture.

Compilation and

assembly.

-marm

Requests that the compiler targets the A32 instruction set. Compilation only.

-mbig-endian

Generates code suitable for an Arm processor using byte-

invariant big-endian (BE‑8) data.

Compilation and

assembly.

1 Compiler Command-line Options

1.2 Summary of armclang command-line options

DUI0774K Copyright © 2014–2017, 2019, 2020 Arm Limited or its affiliates. All

rights reserved.

1-25

Non-Confidential

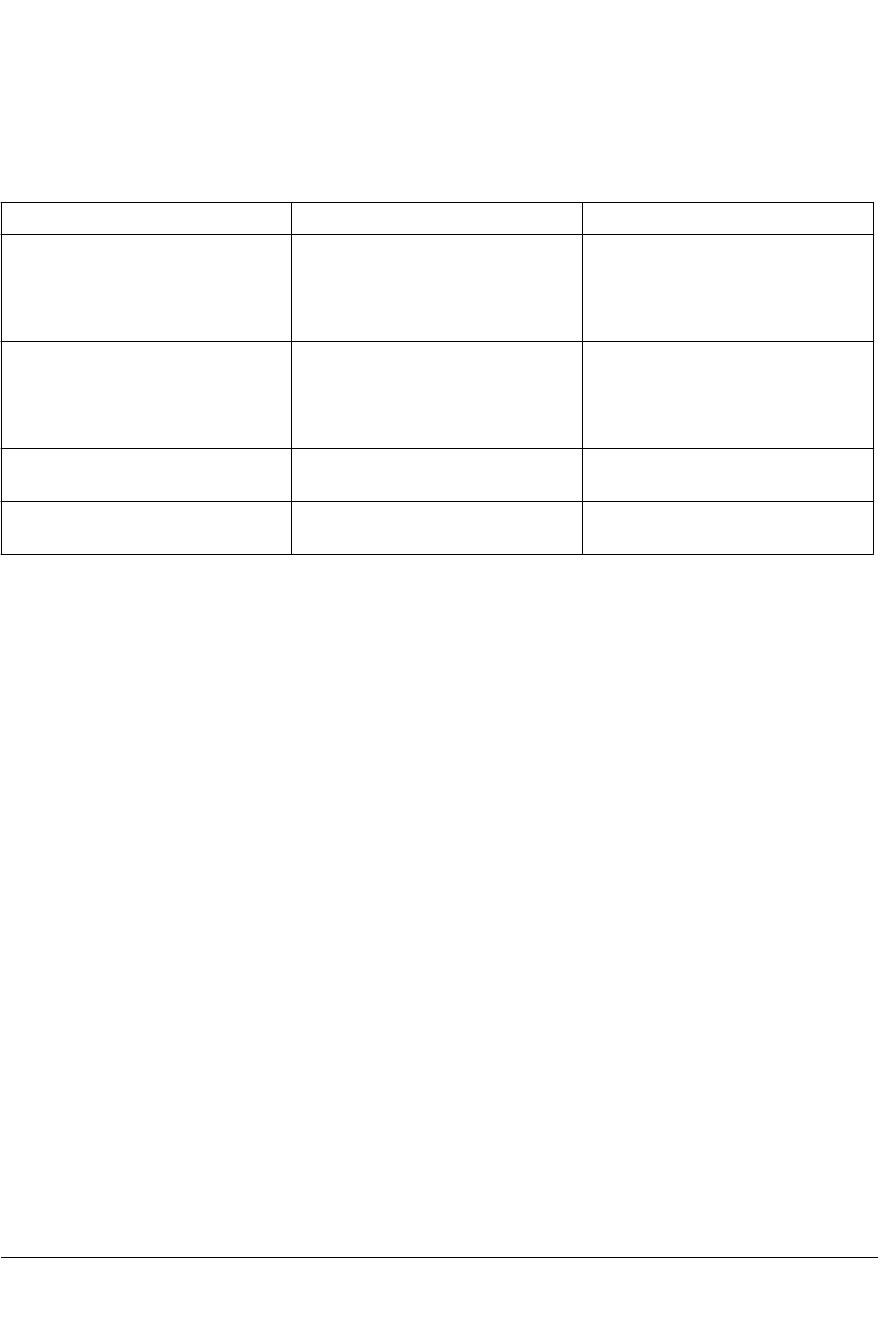

Table 1-1 armclang command-line options (continued)

Option Description Compilation or

Assembly

-mcmse

Enables the generation of code for the Secure state of the

Armv8‑M Security Extensions.

Compilation only.

-mcpu

Targets a specific processor, generating optimized code for that

specific processor.

Compilation and

assembly.

-mexecute-only

Generates execute-only code, and prevents the compiler from

generating any data accesses to code sections.

Compilation only.

-mfloat-abi

Specifies whether to use hardware instructions or software

library functions for floating-point operations, and which

registers are used to pass floating-point parameters and return

values.

Compilation and

assembly.

-mfpu

Specifies the target FPU architecture, that is the floating-point

hardware available on the target.

Compilation and

assembly.

-mimplicit-it

Specifies the behavior of the integrated assembler if there are

conditional instructions outside IT blocks.

Compilation and

assembly.

-mlittle-endian

Generates code suitable for an Arm processor using little-

endian data.

Compilation and

assembly.

-munaligned-access,

-mno-unaligned-access

Enables or disables unaligned accesses to data on Arm

processors.

Compilation only.

-mthumb

Requests that the compiler targets the T32 instruction set. Compilation only.

-nostdlib

Tells the compiler to not use the Arm standard C and C++

libraries.

Compilation only.

-nostdlibinc

Tells the compiler to exclude the Arm standard C and C++

library header files.

Compilation only.

-o

Specifies the name of the output file. Compilation and

assembly.

-O

Specifies the level of optimization to use when compiling

source files.

Compilation only.

-pedantic

Generate warnings if code violates strict ISO C and ISO C++. Compilation only.

-pedantic-errors

Generate errors if code violates strict ISO C and ISO C++. Compilation only.

-Rpass [COMMUNITY] Outputs remarks from the optimization passes made by

armclang. You can output remarks for all optimizations, or

remarks for a specific optimization.

Compilation only.

-S

Outputs the disassembly of the machine code generated by the

compiler.

Compilation only.

-save-temps

Instructs the compiler to generate intermediate assembly files

from the specified C/C++ file.

Compilation only.

-std

Specifies the language standard to compile for. Compilation only.

--target

Generate code for the specified target triple. Compilation and

assembly.

1 Compiler Command-line Options

1.2 Summary of armclang command-line options

DUI0774K Copyright © 2014–2017, 2019, 2020 Arm Limited or its affiliates. All

rights reserved.

1-26

Non-Confidential

Table 1-1 armclang command-line options (continued)

Option Description Compilation or

Assembly

-U

Removes any initial definition of the specified preprocessor

macro.

Compilation only.

-u

Prevents the removal of a specified symbol if it is undefined. Compilation and

assembly.

-v

Displays the commands that invoke the compiler and sub-tools,

such as armlink, and executes those commands.

Compilation and

assembly.

--version

Displays the same information as --vsn. Compilation and

assembly.

--version_number

Displays the version of armclang you are using. Compilation and

assembly.

--vsn

Displays the version information and the license details. Compilation and

assembly.

-W

Controls diagnostics. Compilation only.

-Wl

Specifies linker command-line options to pass to the linker

when a link step is being performed after compilation.

Compilation only.

-Xlinker

Specifies linker command-line options to pass to the linker

when a link step is being performed after compilation.

Compilation only.

-x

Specifies the language of source files. Compilation and

assembly.

-###

Displays the commands that invoke the compiler and sub-tools,

such as armlink, without executing those commands.

Compilation and

assembly.

1 Compiler Command-line Options

1.2 Summary of armclang command-line options

DUI0774K Copyright © 2014–2017, 2019, 2020 Arm Limited or its affiliates. All

rights reserved.

1-27

Non-Confidential

1.3 -c

Instructs the compiler to perform the compilation step, but not the link step.

Usage

Arm recommends using the -c option in projects with more than one source file.

The compiler creates one object file for each source file, with a .o file extension replacing the file

extension on the input source file. For example, the following creates object files test1.o, test2.o, and

test3.o:

armclang --target=aarch64-arm-none-eabi -mcpu=cortex-a53 -c test1.c test2.c test3.c

Note

If you specify multiple source files with the -c option, the -o option results in an error. For example:

armclang --target=aarch64-arm-none-eabi -mcpu=cortex-a53 -c test1.c test2.c -o test.o

armclang: error: cannot specify -o when generating multiple output files

1 Compiler Command-line Options

1.3 -c

DUI0774K Copyright © 2014–2017, 2019, 2020 Arm Limited or its affiliates. All

rights reserved.

1-28

Non-Confidential

1.4 -D

Defines a macro name.

Syntax

-Dname[(parm-list)][=def]

Where:

name

Is the name of the macro to be defined.

parm-list

Is an optional list of comma-separated macro parameters. By appending a macro parameter list

to the macro name, you can define function-style macros.

The parameter list must be enclosed in parentheses. When specifying multiple parameters, do

not include spaces between commas and parameter names in the list.

Note

Parentheses might require escaping on UNIX systems.

=def

Is an optional macro definition.

If =def is omitted, the compiler defines name as the value 1.

To include characters recognized as tokens on the command line, enclose the macro definition in

double quotes.

Usage

Specifying -Dname has the same effect as placing the text #define name at the head of each source file.

Example

Specifying this option:

-DMAX(X,Y)="((X > Y) ? X : Y)"

is equivalent to defining the macro:

#define MAX(X, Y) ((X > Y) ? X : Y)

at the head of each source file.

Related references

1.34 -include on page 1-63

1.66 -U on page 1-104

1.75 -x on page 1-113

Related information

Preprocessing assembly code

1 Compiler Command-line Options

1.4 -D

DUI0774K Copyright © 2014–2017, 2019, 2020 Arm Limited or its affiliates. All

rights reserved.

1-29

Non-Confidential

1.5 -E

Executes the preprocessor step only.

By default, output from the preprocessor is sent to the standard output stream and can be redirected to a

file using standard UNIX and MS-DOS notation.

You can also use the -o option to specify a file for the preprocessed output.

By default, comments are stripped from the output. Use the -C option to keep comments in the

preprocessed output.

Examples

Use -E -dD to generate interleaved macro definitions and preprocessor output:

armclang --target=aarch64-arm-none-eabi -mcpu=cortex-a53 -E -dD source.c > raw.c

Use -E -dM to list all the macros that are defined at the end of the translation unit, including the

predefined macros:

armclang --target=arm-arm-none-eabi -mcpu=cortex-m3 -E -dM source.c

Related references

1.65 --target on page 1-103

1 Compiler Command-line Options

1.5 -E

DUI0774K Copyright © 2014–2017, 2019, 2020 Arm Limited or its affiliates. All

rights reserved.

1-30

Non-Confidential

1.6 -e

Specifies the unique initial entry point of the image.

If linking, armclang translates this option to --entry and passes it to armlink. If the link step is not

being performed, this option is ignored.

See the Arm

®

Compiler toolchain Linker Reference for information about the --entry linker options.

Related information

armlink User Guide

1 Compiler Command-line Options

1.6 -e

DUI0774K Copyright © 2014–2017, 2019, 2020 Arm Limited or its affiliates. All

rights reserved.

1-31

Non-Confidential

1.7 -fbare-metal-pie

Generates position independent code.

This option causes the compiler to invoke armlink with the –-bare_metal_pie option when performing

the link step.

Note

• This option is unsupported for AArch64 state.

• Bare-metal PIE support is deprecated in this release.

Related references

1.21 -fropi, -fno-ropi on page 1-48

1.23 -frwpi, -fno-rwpi on page 1-50

Related information

Bare-metal Position Independent Executables

--fpic armlink option

--pie armlink option

--bare_metal_pie armlink option

--ref_pre_init armlink option

1 Compiler Command-line Options

1.7 -fbare-metal-pie

DUI0774K Copyright © 2014–2017, 2019, 2020 Arm Limited or its affiliates. All

rights reserved.

1-32

Non-Confidential

1.8 -fbracket-depth=N

Sets the limit for nested parentheses, brackets, and braces to N in blocks, declarators, expressions, and

struct or union declarations.

Syntax

-fbracket-depth=N

Usage

You can increase the depth limit N.

Default

The default depth limit is 256.

Related references

7.3 Translation limits on page 7-210

1 Compiler Command-line Options

1.8 -fbracket-depth=N

DUI0774K Copyright © 2014–2017, 2019, 2020 Arm Limited or its affiliates. All

rights reserved.

1-33

Non-Confidential

1.9 -fcommon, -fno-common

Generates common zero-initialized values for tentative definitions.

Tentative definitions are declarations of variables with no storage class and no initializer.

The -fcommon option places the tentative definitions in a common block. This common definition is not

associated with any particular section or object, so multiple definitions resolve to a single symbol

definition at link time.

The -fno-common option generates individual zero-initialized definitions for tentative definitions. These

zero-initialized definitions are placed in a ZI section in the generated object. Multiple definitions of the

same symbol in different files can cause a L6200E: Symbol multiply defined linker error, because the

individual definitions clash with each other.

Default

The default is -fno-common.

1 Compiler Command-line Options

1.9 -fcommon, -fno-common

DUI0774K Copyright © 2014–2017, 2019, 2020 Arm Limited or its affiliates. All

rights reserved.

1-34

Non-Confidential

1.10 -fdata-sections, -fno-data-sections

Enables or disables the generation of one ELF section for each variable in the source file. The default is -

fdata-sections.

Note

If you want to place specific data items or structures in separate sections, mark them individually with

__attribute__((section("name"))).

Example

volatile int a = 9;

volatile int c = 10;

volatile int d = 11;

int main(void){

static volatile int b = 2;

return a == b;

}

Compile this code with:

armclang --target=arm-arm-none-eabi -march=armv8-a -fdata-sections -c -O3 main.c

Use fromelf to see the data sections:

fromelf -cds main.o

...

Symbol table .symtab (17 symbols, 11 local)

# Symbol Name Value Bind Sec Type Vis Size